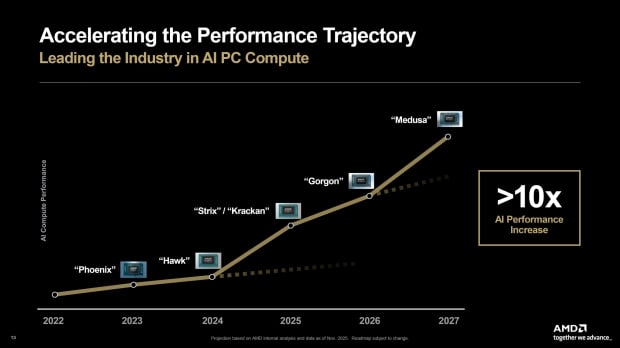

AMD has updated its CPU roadmap, with the company confirming its next-gen Zen 6 processors for 2026, with the new CPU roadmap including its next-gen "Medusa" CPUs based on Zen 6.

AMD confirmed what the leaks have suggested for a while now, with more on that in the links above, with "Gorgon" and "Medusa" CPUs launching in 2026 and 2027, respectively. Gorgon Point APUs are still based on the current Zen 5 CPU, with an upgraded RDNA 3.5-based GPU like its Strix Point and Strix Halo APUs.

However, when it comes to the new codename "Medusa" chips, Medusa Point and Medusa Halo APUs will feature next-gen Zen 6 CPU cores, a next-gen RDNA 5-based GPU, and next-gen XDNA for AI workloads in 2027.

In leaks that we've covered previously, AMD's flagship Medusa Halo APU would feature 24C/48T of Zen 6 CPU power, 48 CUs of RDNA 5 GPU power, and either LPDDR6 or LPDDR5X memory controller, possibly offering up to GeForce RTX 5070 Ti levels of gaming performance.

AMD's next-gen Zen 6 processors leaked so far:

Olympic Ridge & Gator Range: AM5 + FL1 sockets, TSMC N2X CCD chiplets + N3P IOD chiplet (or N6)

- N3P IOD = 2 x 12-core Zen 6 + 2-core Zen 5 LP = 26 cores total (24+0+2) targeting over 6.0GHz clock speeds (6nm IOD likely has no LP cores)

- There are references to both a TSMC N3P IOD without a decent iGPU, and also a TSMC N6 IOD with weaker (or no) graphics and less features. It's plausible that AMD will use N6 IODs for budget AM5 SKUs.

- 128-bit DDR5 memory controller

Medusa Point Big (MD51): FP10 socket, TSMC N2P CCD chiplet + N3P IOD chiplet (and/or N3P monolithic)

- Chiplet variant = 1 x 12-core Zen 6 chiplet + 2-core Zen 5 LP = 14 cores total (12+0+2) (may get Zen 5 LP instead of Zen 6 LP for time to market)

- Monolithic variant = 4-core + 8-core Zen 6c + 2-core Zen 5 LP = 14 cores total (4+8+2) (may get Zen 5 LP instead of Zen 6 LP for time to market)

- 8-16 CU RDNA 4 or 3.5 (+) iGPU (both architectures are referenced as possibilities, and there are different CU counts referenced between documents of different variants)

- 128-bit LPDDR5X memory controller

- There are references to both an "N2 powderdorn CCD" for "AI 9 products" and a "monolithic N3P die" for "AI 7 / AI 5" class products (it seems "MD51" includes both high-end and mid-range variants)

Medusa Point Little (MD52): FP10 socket, TSMC N3P monolithic

- 2 or 4-core Zen 6 + 4-core Zen 6c = 8-10 cores total (2 or 4+4+2) (AMD has not yet decided if they want to go with 2 or 4 "full" Zen 6 cores)

- 4 CU RDNA 4 or 3.5 (+) iGPU (both architectures are referenced as possibilities, and there are different CU counts referenced between documents of different variants)

- 128-bit LPDDR5X memory controller

- "MD52" is specifically listed as targeting "AI 5" and "AI 3" class products

Bumblebee (MD53): FP10 and/or FP8 socket: TSMC N3C monolithic

- 2-core Zen 6 + 2-core Zen 6c + 2-core Zen 6 LP = 6 total cores (2+2+2)

- 2-4 CU RDNA 4 or 3.5 (+) iGPU (both architectures are referenced as possibilities)

- 128-bit LPDDR5X memory controller

- "MD53" is specifically listed as targeting the "budget laptop" market

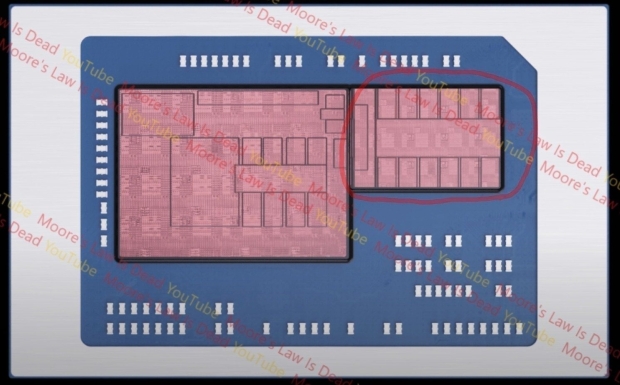

Medusa Halo (MD5H): FP12 + FP11 sockets, TSMC N2P core chiplets + N3P IOD chiplet

- 2 x 12-core Zen 6 + 2-core Zen 6 LP = 26 cores total (24+0+2)

- 48 CU RDNA 5 or 4 or 3.5 (+) iGPU (yes, there are references to possibly redefining the iGPU with RDNA 4 or RDNA 5 IP)

- RDNA 5 is targeting a very late 2025 or 2026 tapeout (it's not certain yet), and thus aligns with MD5 Halo maybe getting RDNA 5)

- 384-bit LPDDR6, 256-bit LPDDR5X memory controller (LPDDR6 has 50% more bits per channel)

- There is reference to (Little Halo) with a 192-bit LPDDR6 / 128-bit LPDDR5 memory controller and 24 CUs