Taiwan Semiconductor Manufacturing Co. (TSMC) has just unveiled its updated process technology roadmaps, some new information on the next-gen N3 process nodes, and more at its 2022 TSMC Technology Symposium.

TSMC unveiled its new FinFlex technology for N3, which allows chip designers -- like Apple, AMD, NVIDIA, Qualcomm, and others -- to choose the best options for the key functional blocks on the same die, using the same design tool set.

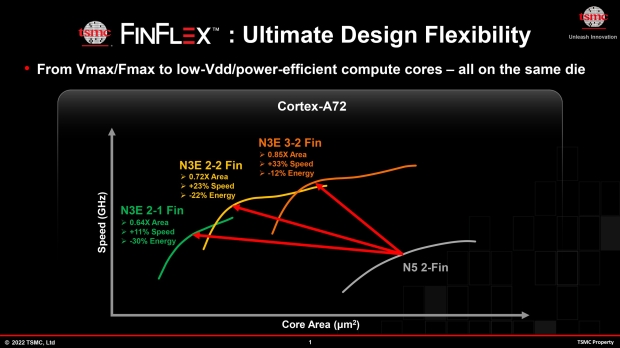

Godfrey Cheng, Head of Global Marketing, TSMC, explained on the official TSMC website that TSMC's new FinFlex technology: "extends the product performance, power efficiency and density envelope of the 3nm family of semiconductor technologies by allowing chip designers to choose the best option for each of the key functional blocks on the same die using the same design toolset. These options include a 3-2 FIN, 2-2 FIN and 2-1 FIN configuration with the following characteristics".

- Read more: TSMC's next-gen 3nm yields are so good, production is starting earlier

- Read more: TSMC talks more about 3nm, hitting nails into Intel's Big Blue coffin

- Read more: TSMC to spend tens of billions more on US-based 3nm chip factories

- Read more: TSMC will make Intel CPUs on 3nm in 2022, largest order of 3nm process

- Read more: TSMC is so ahead of the game, Samsung might not catch up until 2030

- 3-2 FIN - Fastest clock frequencies and highest performance for the most demanding compute needs

- 2-2 FIN - Efficient Performance, a good balance between performance, power efficiency and density

- 2-1 FIN - Ultra Power Efficiency, lowest power consumption, lowest leakage and highest density

We're already seeing the start of this with hybrid CPUs, where there are now CPUs with high-performance CPU cores that are matched with power-efficient CPU cores + and then GPU cores and I/O blocks. But now with the introduction of TSMC's new FinFlex in N3 technology, product designers can "choose the best FIN configuration for each of these functional blocks, optimizing each block without affecting others, all on the same die".

- Read more: AMD details Zen CPU roadmap: Zen 5 with V-Cache on 4nm + 3nm in 2023

- Read more: Apple M2 Max: 12-core CPU, 38-core GPU, made on TSMC next-gen 3nm

- Read more: TSMC to build Intel's new 3nm CPUs at new site in northern Taiwan

- Read more: AMD's next-gen Zen 4 Dense (Zen 4D) tech: fights Intel Hybrid CPU tech

- Read more: AMD details its next-gen 3D V-Cache stacking technology