AMD has better detailed its next-gen 3D V-Cache stacking technology, where at the exciting but all-digital Hot Chips 33 symposium the company teased its current, and even future 3D stacking technologies.

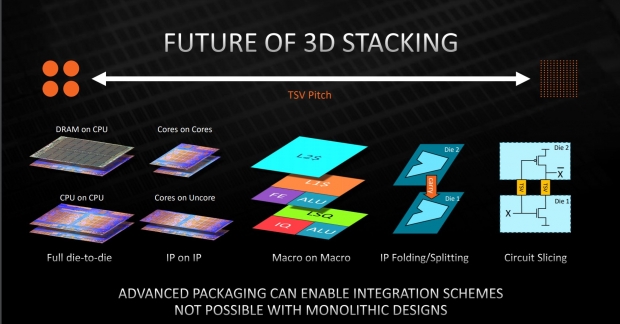

As the TSV (Through Silicon Via) which is a vertical inter-wafter or inter-die connection -- has the amount of bonds increased, the 3D V-Cache technology will be pushed into more complex 3D stacking designs. Over the years we'll see 3D stacking of full die-to-die stacking, which will usher in a new world of more DRAM on CPUs, or even more CPUs on CPUs -- yeah.

AMD showed that the future of 3D stacking will allow for more DRAM on CPUs, more CPUs on CPUs, IP on IP, and so much more. AMD explains that "advanced packaging can enable integration schemes not possible with monolithic designs" and this is the biggest point here -- MCM and MCD designs >>> monolithic designs.

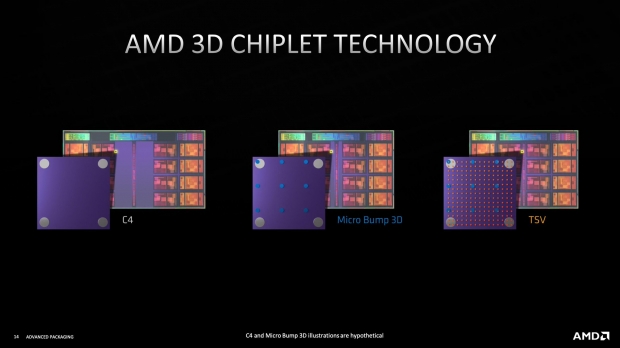

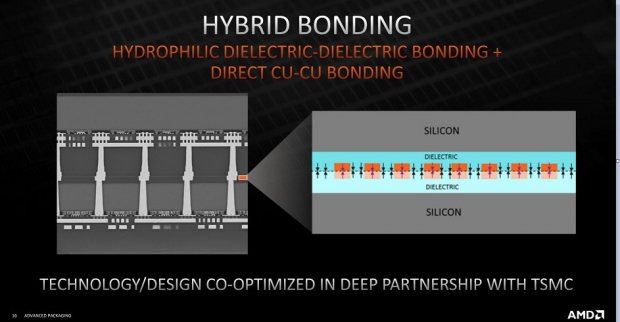

AMD is using a micron bump pitch of 9 microns here, denser than competitor Intel and its in-house Foveros Direct technology at 10 microns -- something that Intel won't have ready until at least 2024. While AMD will be wielding its 9-micron bump pitch sword soon, Intel is lagging behind considerably with 50-micron bump pitch once AMD has its 3D V-Cache technology available in chips in the coming months.

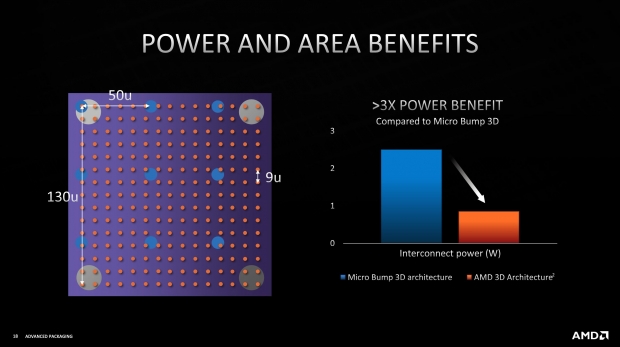

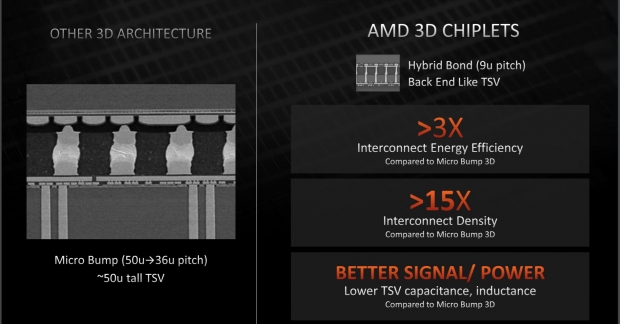

There's going to be some major power efficiency with the new AMD 3D V-Cache technology over the Micro Bump 3D architecture, with 3x power efficiency promised.

AMD has over 3x the interconnect energy efficiency with its 3D V-Cache technology over Micro Bump 3D technology, an insane 15x interconnect density increase, and overall better signal and power with lower TSV capacitance, inductance over Micro Bump 3D.

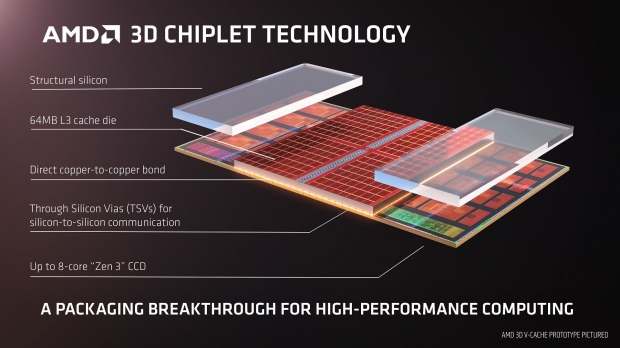

The overview at the bottom is great, as it shows you how the packaging goes together -- the structural silicon, 64MB of L3 cache die, direct copper-to-copper bond, Through Silicon Vias (TSVs) for silicon-to-silicon communication, and up to an 8-core Zen 3 CCD.

It's bloody impressive to see, and I can't wait to have it in my labs running in future Ryzen CPUs coming by the end of next year and much more so in 2022 and beyond.