AMD has been rumored for quite a while that it was working on a multi-chiplet gaming GPU, with a new patent fueling these rumors in the battle of GPUs against NVIDIA.

In a new video shared by coreteks, we're hearing that AMD has recently secured a new multi-chiplet GPU patent that could solve the latency issues using a 'Smart Switch'. MCM (Multi-Chiplet Module) isn't new, as they're used outside of the gaming GPU market, but there are limitations of monolithic GPU designs that MCM can solve.

AMD used an MCM design approach for its Instinct MI200 series AI accelerators, stacking multiple chiplets onto a single package, including the GPCs (Graphics Processing Cores), HBM memory stack, and the I/O die. However, AMD used a different approach with its Instinct MI350 series AI chips, and this could be the foundation of its multi-chiplet-based consumer gaming GPUs according to coreteks in his new video.

One of the biggest hurdles of a chiplet design for gaming GPUs is the increased latency, as frames are intolerant to long-distance data hops, and in order to get around this road block, AMD has to find a solution that reduces the gap between data and computation, making them as close as possible.

The new patent that AMD has secured is described in coreteks' video, revealing that AMD might have indeed cracked the code when it comes to the future of a multi-chiplet gaming GPU. The patent discloses details about CPUs instead of GPUs, but the text and mechanism tease that it's targeted towards being used with a graphics card.

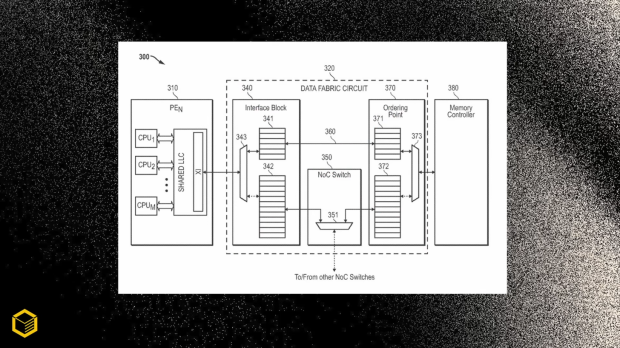

One of the main points of the new patent is the "data-fabric circuit with a smart switch" that would bridge communications between the compute chiplets and memory controllers. This is very similar to AMD Infinity Fabric, but scaled down for consumer GPUs as AMD can't use HBM memory dies on a gaming card.

This switch would optimize memory access by first comparing whether a request for a graphics task requires task migration or data replication, with nanosecond-scale decision latency. With the problem of data accessing solved, the patent proposes to have GCDs with L1 and L2 cache, similar to what we see with AI GPUs.

However, an extra L3 cache (or stacked SRAM) can be accessed through the smart switch, connecting to all of the GCDs. This will reduce the need to access global memory, acting as a shared staging zone between the chiplets, similar to how AMD does it with their market-leading 3D V-Cache technology. There's also stacked DRAM in the mix, acting as a foundation for the MCM-based design.

We are reaching the limitations of monolithic GPU designs, so a huge switch up to a multi-chiplet GPU design would give AMD the opportunity to better compete against NVIDIA, which has been leading the high-end GPU market for many years now.

It isn't easy, as there are complications and intricacies with multi-chiplet designs -- something AMD experienced with RDNA 3, which was driven by the latency introduced by the chiplet interconnect -- but using a smart switch approach with shared L3 cache, AMD could have this solved for gamers.

UDNA 5 is the next GPU architecture from AMD, where we could be teased -- or even introduced -- to a multi-chiplet Radeon GPU. Exciting times ahead!