AMD isn't too far from launching its newly rebranded Ryzen AI 300 series "Strix Point" APUs, with David Huang testing the new Ryzen AI 9 365.

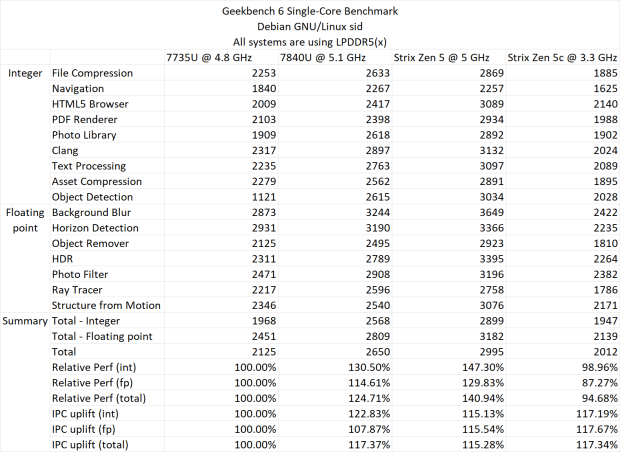

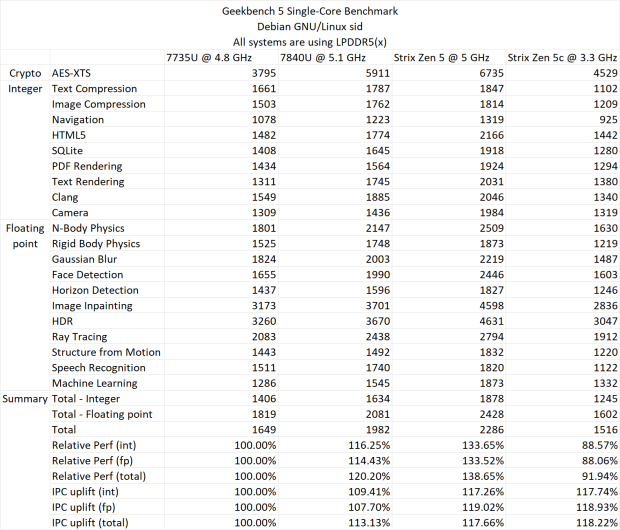

Huang has gotten his hands on some pre-launch Ryzen AI 300-powered devices. His review looks at Zen 5's architectural improvements, with detailed, high-level comparisons between AMD's previous-gen Zen 3, current-gen Zen 4, and next-gen Zen 5 architectures. He even includes some separate testing on the Zen 5c dense cores on the new Strix Point APU.

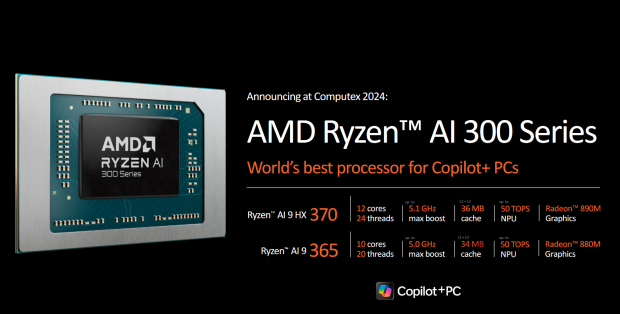

The new AMD Ryzen AI 9 365 features 10 cores and 20 threads of Zen 5 power, boosting up to 5.0GHz (4 x Zen 5 cores and 6 x Zen 5c cores). AMD hasn't confirmed the boost clocks of the Zen 5c cores, but David's early testing has the Zen 5c cores at 3.3GHz, with David noting that both Zen 5 and Zen 5c cores were operating at their respective frequencies without affecting one another. In his testing, David used a product with 32GB of LPDDR5X memory at 7500MT/s.

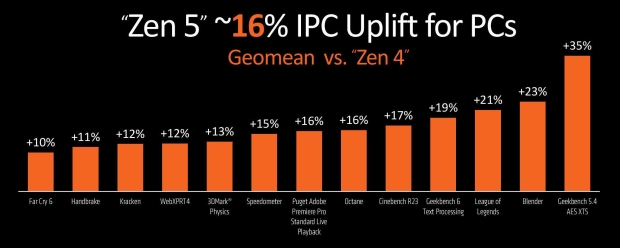

David ran some SPEC CPU tests with all processors locked to 4.8GHz across the board, showing that the new Zen 5 chip has 22% relative improvements over Zen 4, with an estimated 9.7% IPC improvement, with all architectures compared against their respective predecessors. Geekbench 6 single-core performance was also looked at, with the next-gen Zen 5 architecture showing an impressive 15% IPC improvement over Zen 5, while Geekbench 5 saw an IPC improvement of 17.6%.

- Read more: AMD's next-gen Strix Point APU renamed again: Ryzen AI 300 series to fight Intel Core Ultra 200

- Read more: AMD Ryzen AI 300 and Intel Lunar Lake CPUs will be launching WITHOUT their Copilot+ AI features

- Read more: AMD's high-end Ryzen AI 'Strix Halo' APUs spotted: 16C/32T Zen 5, 120W TDP, 64GB memory

- Read more: AMD's new Strix Point APU are reportedly called Ryzen AI 9 HX 170, big name changes with Zen 5

AMD itself promised 16% performance gains in IPC with Zen 5, so with David's early testing, it looks like AMD is sticking to that very closely.

If you want to geek out more with Zen 5, David did some inter-core latency tests, microarchitecture features, instruction fetching, decoding, and micro-op cache. Check out the full testing here.