AMD's next-generation high-end Ryzen AI "Strix Halo" APUs have turned up in new shipping manifestos, featuring up to 64GB capacities and up to 120W TDPs.

The shipping manifestos were noticed by "nbd.ltd" and @harukaze5719, with multiple shipments of the same APU that would've been sent out for evaluation and testing purposes. These manifestos show the Maple DAP reference evaluation platform, which is available in both 32GB and 64GB memory capacities.

The Maple DAP reference systems feature 32GB or 64GB of pre-soldered memory, set by AMD, unlike Intel which is using on-package memory with its next-generation Lunar Lake CPUs.

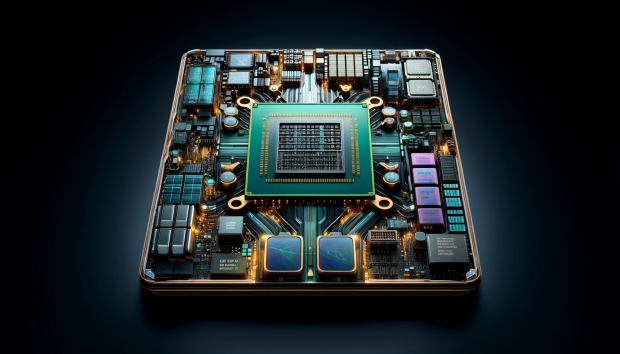

Inside, the new Strix Halo APUs uses a chiplet-based design, with up to 3 x dies, 2 x CCDs, and 1 x GCD. The CCDs will house up to 16 cores and 32 threads of next-gen Zen 5 processing power, with 16MB of L2 cache and 32MB of L3 cache per CCD. This means Strix Halo has a total of 64MB of L3 cache on the top (two CCD) chips.

GPU-wise, Strix Halo features an integrated RDNA 3+ graphics architecture with 20 WGPs or 40 Compute Units, with an additional 32MB of MALL cache on-board the IOD that will remove bandwidth bottlenecks for the integrated GPU.

AMD's new Strix Halo APUs will support LPDDR5X-8000 (256-bit) memory, with an XDNA 2-based NPU for AI workloads offering over 70 TOPS of performance. We'll have 70W TDPs (55W cTDP) and peak ratings of up to 130W for Strix Halo.

AMD Ryzen AI HX Strix Halo Expected Features:

- Zen 5 Chiplet Design

- Up To 16 Cores

- 64 MB of Shared L3 cache

- 40 RDNA 3+ Compute Units

- 32 MB MALL Cache (for iGPU)

- 256-bit LPDDR5X-8000 Memory Controller

- XDNA 2 Engine Integrated

- Up To 60 AI TOPS

- 16 PCIe Gen4 Lanes

- 2H 2024 Launch (Expected)

- FP11 Platform (55W-130W)