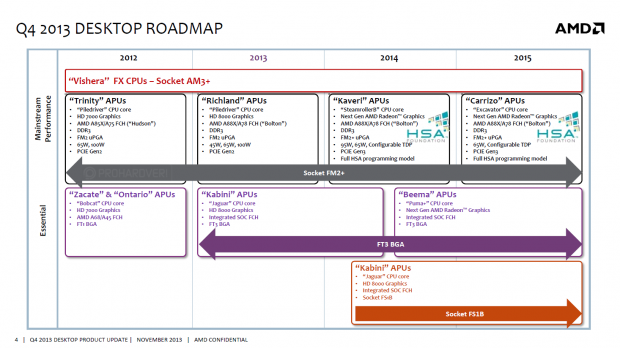

It seems that AMD is working on a new APU using 28nm process and stacked DRAM, codenamed 'Carrizo'. It is said that these APUs will benefit from HBM (Higher Bandwidth Memory) implementation compared to current DIMM slot counterparts.

Though the reports are unconfirmed, it is known that AMD is collaborating with Hynix to make stacked DRAMs. The HBM provides higher bandwidth which will benefitted by the APU especially by the onboard graphics core. The APU will be made with 28nm process, but the onboard HBM die will be based on 20nm process. Its speculated that Carrizo's APU core die size is smaller than Kaveri.

HBM can provide maximum bandwidth of 128-256GB/s, which will prove to be a better implementation over DDR4 support. These APUs will most likely use the FM2+ socket and maintains 65w TDP envelope. If AMD incorporates on package DRAM solution, it will allow higher speeds for the memory and have lesser latency even compared to DDR4 implementation and it would cost lesser than integrating L3 cache. Whether the stacked DRAM be implemented in all of Carrizo APU lineups and feasibility especially for low-cost APUs is currently unknown.