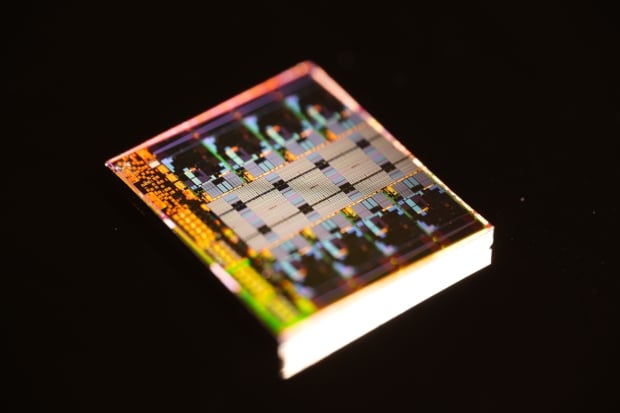

I'm a huge fan of high-res die shots of new chips, with Fritzchens Fritz pulling out the microscope and posting some truly beautiful die shots of AMD's newly-launched Zen 5-powered Ryzen 9000 series "Granite Ridge" CPUs. Check them out:

The new die shots of the Ryzen 9000 series CPUs gives us a (much) closer look of the new Zen 5 architecture, and what AMD has planned for the future (hint: its upcoming Ryzen 9000X3D series CPUs with 3D V-Cache). Fritzchens Fritz had to sacrifice his Zen 5 chip because its CCD needed to be extracted to get the close-up shots of the die.

AMD's new Ryzen 5 9600X processor was used in the breakdown, packing a single Zen 5 CCD and a single IOD and the pictures are absolutely gorgeous, I truly nerd out of these shots. So, Fritzchens Fritz, if you're reading this... hat tip, good sir. He noted on X that this time AMD's new Zen 5 "Granite Ridge" CPUs offer "interesting changes" for the 3D V-Cache in upcoming Ryzen 9000X3D series processors.

- Read more: Apple A18 Pro, A18 SoC die sizes compared: built on TSMC N3E node

- Read more: This is what 2.5D aka CoWoS advanced packaging looks like: GPU logic die, HBM, interposer

- Read more: AMD's new Ryzen 9000 series CPU delidding 'goes wrong' with a cracked die

- Read more: Check out this beautiful die shot of AMD's new Ryzen AI 300 'Strix Point' APU

We know from publicly available information that each of AMD's new Zen 5 CCDs -- Eldora -- has a die size of 70.6mm2 and packs 8.315 billion transistors, fabbed on TSMC's new N4P process node. You can see the die show with annotation from Fritzchens Fritz.

The AMD Zen 5 CCD on the Ryzen 9000 series "Granite Ridge" CPUs is the only of the two dies that has been changed over the Zen 4 "Raphael" CPUs, while the IO die is the same, and is made on the TSMC 6nm process node. The positioning of the TSVs within the L3 cache might stress the CCD itself, so speculation teases AMD might use a 2-Hi stacked 3D V-Cache design to counter these issues.

This opens up some space for increased 3D V-Cache amounts, but we've been hearing rumors that we're to expect the same amount of 3D V-Cache on the upcoming Zen 5-based Ryzen 9000X3D processors as their Zen 4-based Ryzen 7000X3D processor counterparts.

AMD choosing the route of boosted amounts of 3D V-Cache on Ryzen 9000X3D series processors is a more fragile process, creating new issues and increasing costs... something AMD doesn't want to do after the limped Zen 5 launch, and Intel's virutally-here Core Ultra 200 series "Lunar Lake" CPUs.

CCD:

- 69.973mm² (with scribe lines)

- 67.242mm² (w/o scribe lines)

- 66.462mm² (w/o seal ring)

- 3.723mm² (Core w/o L2$)

- 4.772mm² (Core with L2$)

- 6.836mm² (Core with L3$)

- 15.689mm² (L3$ area)