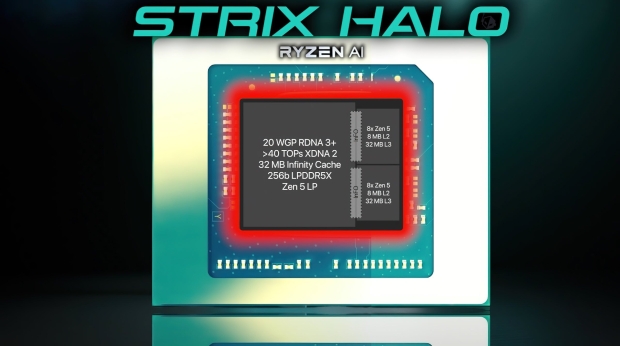

AMD's next-gen "Strix Halo" Zen 5-based APU has been pictured on Chiphell, showing off its chiplet-based deisgn, using 256-bit LPDDR5X memory.

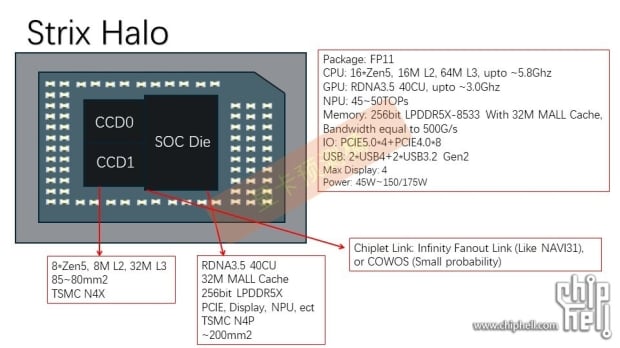

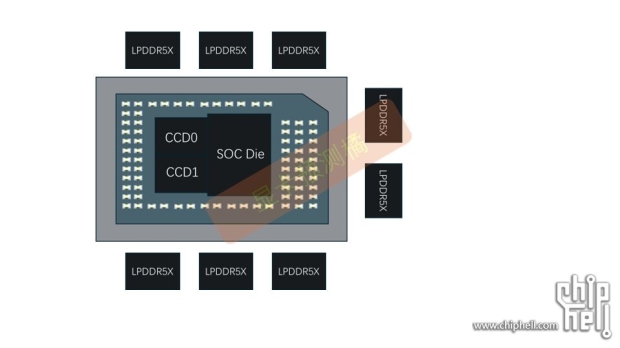

The new Strix Halo APU will feature a chiplet-based design, with one or two Zen 5 CCDs and a huge SoC die that features an oversized integrated RDNA 3+ GPU, and 256-bit LPDDR5X memory controllers not found on the cIOD. AMD is aiming at CPU and GPU performance that competes with Apple's M3 Pro and M3 Max SoCs, at comparable PCB and power consumption.

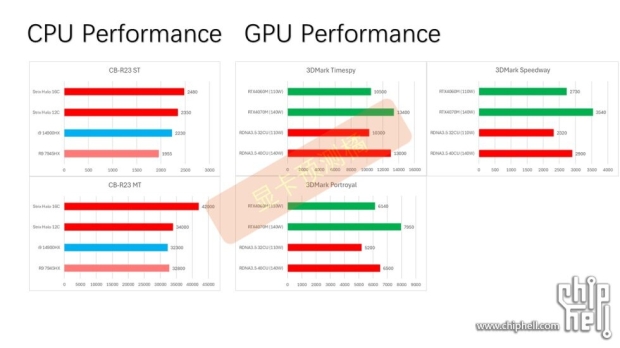

AMD is using an integrated RDNA 3+ GPU in its next-gen Strix Halo APU, with a huge 40 Compute Units that works out to 2560 Stream Processors, 80 AI accelerators, 40 Ray accelerators, 160 TMUs, and an unknown amount of ROPs, with GPU clock speeds of up to 3.0GHz.

We should expect Strix Halo GPU performance to be somewhere between NVIDIA's GeForce RTX 4060M and RTX 4070M laptop GPUs.

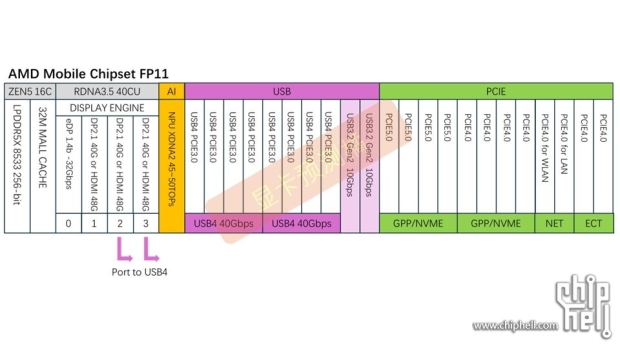

AMD is reportedly using a 256-bit LPDDR5X-8533 memory interface, which will provide an effective cached bandwidth of around 500GB/sec. The memory controllers are joined by 32MB L4 cache on the SoC die, while the NPU on Strix Halo will be the same XDNA 2-based NPU that we will see on the upcoming Strix Point APUs.

AMD's new Strix Halo APU has an SoC I/O that supports PCIe Gen5, with 12 Gen5 lanes, 4 aimed at an M.2 NVMe slot, and 8 PCIe 5.0 lanes for a discrete graphics card.

These PCIe 5.0 lanes can be used for additional M.2 SSD slots, if you're only using the integrated RDNA 3+ GPU and not a discrete GPU. There's also integrated 40Gbps USB4, and 20Gbps USB 3.2 Gen2.

We can expect up to 16 cores and 32 threads of next-generation Zen 5 CPU power, with 32MB of L3 cache per CCD for total of 64MB of L3 cache. The CCDs are connected to the SoC die through conventional IFOP (Infinity Fabric over package), just like "Fire Range" and "Granite Range" offerings from AMD.

AMD Ryzen AI HX Strix Halo Expected Features:

- Zen 5 Chiplet Design

- Up To 16 Cores

- 64 MB of Shared L3 cache

- 40 RDNA 3+ Compute Units

- 32 MB MALL Cache (for iGPU)

- 256-bit LPDDR5X-8000 Memory Controller

- XDNA 2 Engine Integrated

- Up To 60 AI TOPS

- 16 PCIe Gen4 Lanes

- 2H 2024 Launch (Expected)

- FP11 Platform (55W-130W)