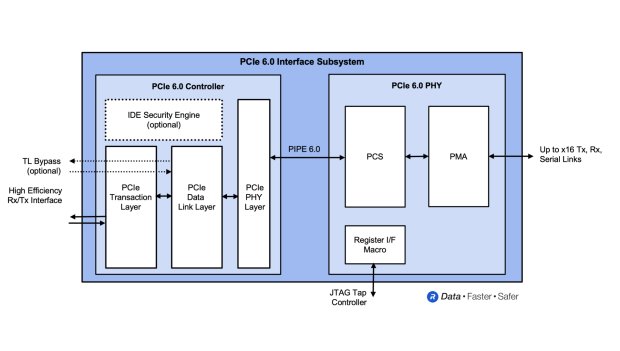

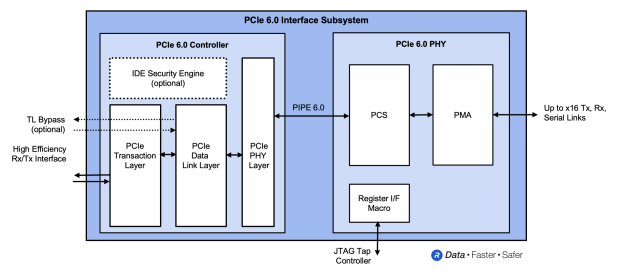

Rambus has just announced the availability of its next-gen PCIe 6.0 Interface Subsystem that packs PHY and controller IP, with the latest version of the Compute Express Link (CXL) specification version 3.0 also supported.

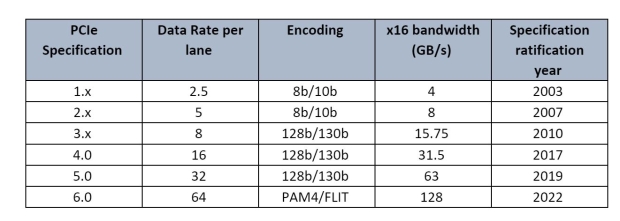

The new Rambus PCIe 6.0 Interface Subsystem features up to 64 GT/s ready to drive next-gen data centers and AI systems, with Rambus saying its new PCIe 6.0 Interface Subsystem is fully optimized to meet the needs of advanced heterogenous computing architectures.

There's a PCIe controller that has an Integrity and Data Encryption (IDE) engine that is dedicated to protecting the PCIe links and the valuable data transferred over them.

- Read more: Rambus announces PCIe 6.0 controller: pumps up to 64GB/sec speeds

- Read more: Synopsys first with complete IP solution for PCIe 6.0 tech in Q3 2021

- Read more: PCIe 7.0 specs announced: SSDs will ramp up to 128GB/sec insanity

- Read more: PCIe 6.0 announced: lands in 2021, just as PCIe 4.0 arrives

Scott Houghton, general manager of Interface IP at Rambus explains: "The rapid advancement of AI/ML and data-intensive workloads are driving the continued evolution of data center architectures requiring ever higher levels of performance. The Rambus PCIe 6.0 Interface Subsystem supports the performance requirements of next-generation data centers with best-in-class latency, power, area, and security".

PCI Express layer

- Designed to the latest PCI Express 6.0 (64 GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1/3.0 (8 GT/s), and PIPE 6.x (8, 16, 32, 64 and 128-bit) specifications

- Supports SerDes Architecture PIPE 10b/20b/40b/80b width

- Supports original PIPE 8b/16b/32b/64b/128b width

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports multiple virtual channels (VCs) in FLIT and non-FLIT modes

- Supports Endpoint, Root-Port, Dual-mode, Switch port configurations

- Supports PCIe 6.0 to PCIe 1.0 speeds

- Supports Forward Error Correction (FEC) - Lightweight algorithm for low latency

- Supports L0p Low Power mode

- Up to 4-bit parity protection for data path

- Supports Clock Gating and Power Gating

- RAS features include LTSSM timers override, ACK/NAK/Replay/UpdateFC timers override, unscrambled PIPE interface access, error injection on Rx and Tx paths, recovery detailed status, and much more, allowing for safe and reliable deployment of IP in mission-critical SoCs

Rambus PCIe 6.0 Interface Subsystem key features:

- Supports PCIe 6.0 specification including 64 GT/s data rate and PAM4 signaling

- Implements low-latency Forward Error Correction (FEC) for link robustness

- Supports fixed-sized FLITs that enable high-bandwidth efficiency

- Backward compatible with PCIe 5.0, 4.0, and 3.0/3.1