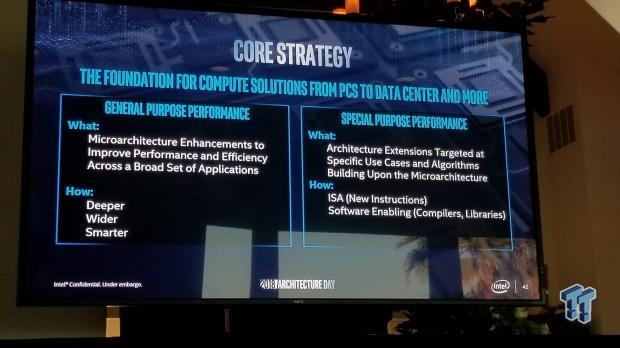

Intel recently detailed their vision for the future of their Core strategy during their 2018 Architecture day.

They are looking forward and looking at three points to really put them ahead; they are going to go deeper, wider, and smarter, and we will explain what those mean in a second. For now, Intel is aiming at their advantages including single core performance, their ISA, and software improvements.

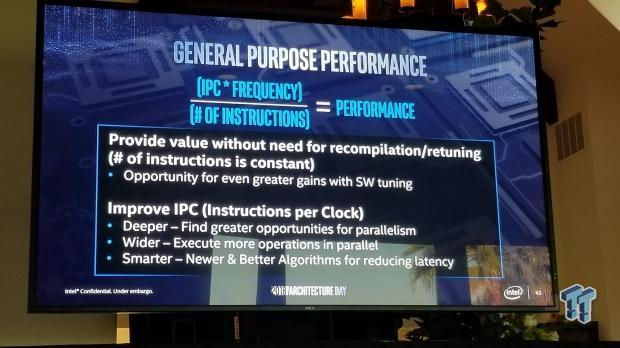

Intel also wanted us to know how they define performance. IPC times frequency divided by the number of instructions seems like a good equation for us. Now, to improve IPC, which would be the first large increase since Skylake launch, Intel is going to do a few things. For starters they will go deeper; meaning they will increases parallelism. Then they will go wider, which means they will try and execute more instructions in parallel, to provide more unit capabilities (increase ports). The last thing is to go smarter, which means reducing latency and improving things such as branch prediction.

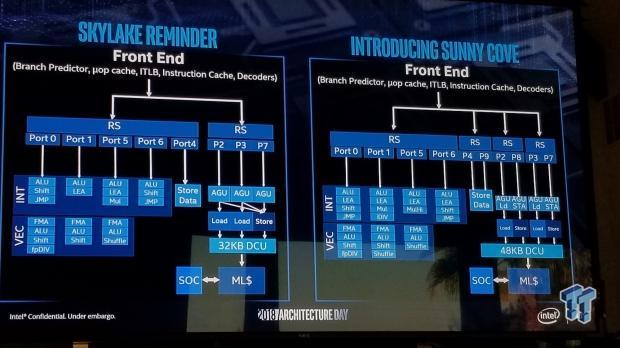

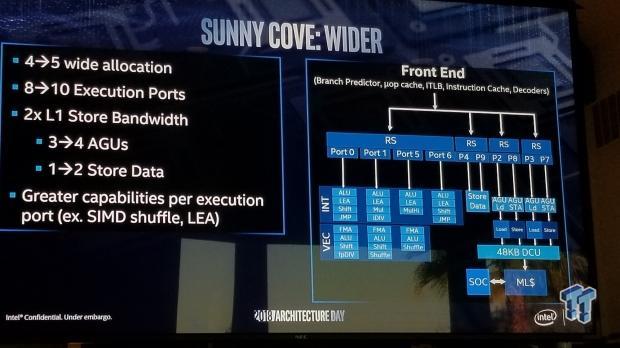

Okay, let's compare Skylake and Sunny Cove. Sunny Cove is basically the first new microarchitecture since Skylake, which hasn't changed much over the past few generation (Coffe Lake, Kaby Lake, etc.). For starters there are more ports, 10 instead of 8. We also get and increased number of store units, and increased cache, and added capabilities within the integer execution units.

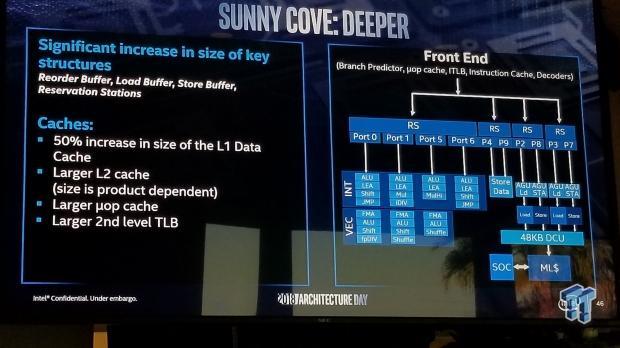

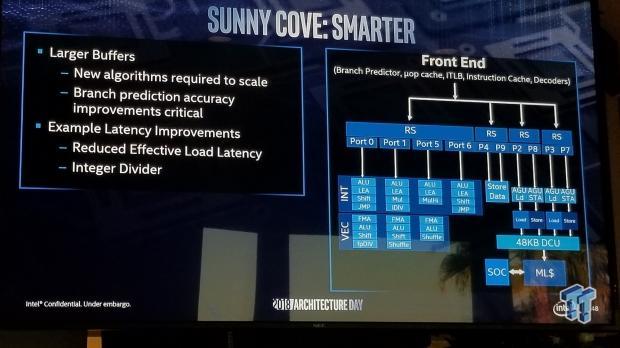

Let's go deeper. For starters, Intel hasn't changed their L1 cache size in ages (seriously ages), but now they are increasing is 50%, which is not just very costly in regards to production cost, but should greatly improve the ability for the CPU's front end to be fed. We also get increases in L2 cache, a larger uop cache, and a larger 2nd level translation lookup buffer. Intel has also increased the size of their re-order buffer, load buffer, store buffer, and reservation stations (schedulers, shown as "RS" on the slides).

Let's go wider! So we have a larger scheduler, up to 10 execution ports from 8, double the L1 store bandwidth, an increase from 3 to 4 AGUs that then results in an extra store. We also get added port execution capabilities such as SMID shuffle and LEA in regards to integer execution.

Sunny Cove is also smarter, it uses new algorithms that are required to scale and branch prediction has been improved. The accuracy of the branch predictor has been improved, which is a great thing since it will result in less flushes of cache. Latency has also been improved.

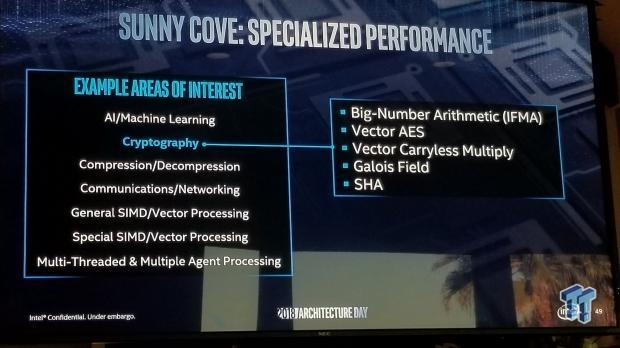

Let's also talk specialization. Intel has improved the cryptographic capabilities of the CPU in regards to IFMA, vector AES, vector carryless multiple, Galois Field, and SHA.

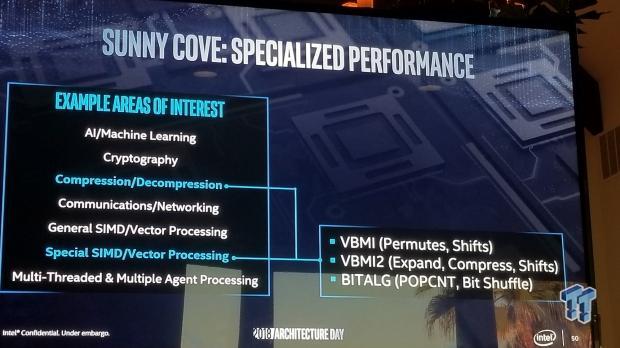

The CPU microarchitecture will also get improvements compression/depression, as well as certain vector processing in regards to instruction set architecture (ISA).

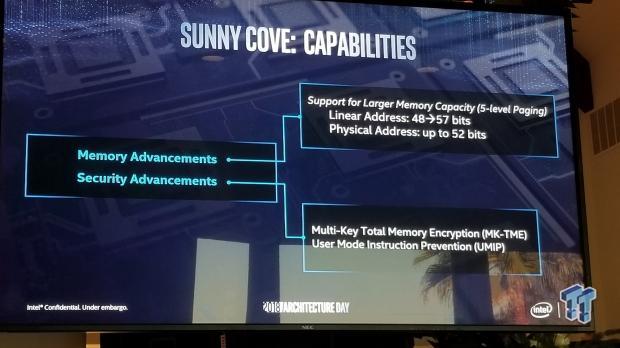

Intel is also focusing on memory and security (two of their six new pillars), and they have increased address size for memory and encryption for security.

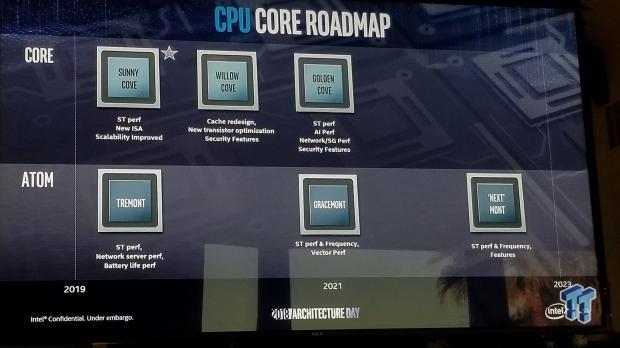

Here we have Intel's future roadmap for its CPUs, we can see that Sunny Cove is just the beginning.