Computex 2014 - Error rates are increasing as NAND manufacturers shrink lithography. This requires SSD controller innovation to provide stronger error correction without negative performance ramifications. Even with a standard HDD, data read directly from the media is rarely decipherable without post-processing, such as BCH error correction. As we move towards smaller NAND with much higher bit-error rates, manufacturers are scrambling to develop error-reduction technologies. Some approaches occur prior to, and during, drive operations. However, there are inevitable errors that require correction after command completion.

The method currently favored is BCH ECC. BCH can handle the error rates of current NAND, but all error correction methods add additional processing overhead to command latency. As the error rates have increased, designers have simply implemented more robust BCH ECC. The problem is the diminishing point of returns, and more robust BCH adds too much overhead on thee low-wattage controllers utilized in SSDs. Eventually there is a point where the controller can no longer correct the errors, and the data is corrupted.

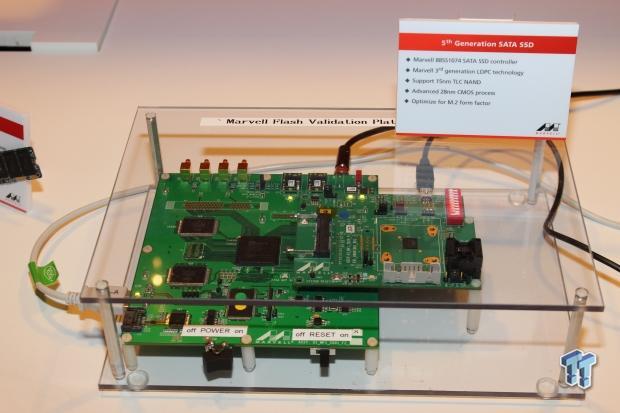

Enter LDPC. Enabling a more efficient algorithm, that is also adaptive, provides intelligent error correction with less overhead. This provides more error correction power with less impact on SSD performance. In the video above Marvell is intentionally injecting errors into the path of the controller, thus simulating errors encountered during SSD use. A simple view of the two video streams side-by-side illustrates the vast difference in ECC performance between the two methods. Other manufacturers are also utilizing LDPC technology, such as SandForce and Adaptec. There are varying levels and complexity to LDPC algorithms, and until products reach the market it will be hard to determine which works best. It is clear that Marvell has a great grasp of the technology, and the increased performance will allow the use of smaller NAND lithographies with no impact to data integrity.