Sony filed a new patent that suggests a higher-end PS5 Pro console with dual GPUs (as well as a myriad of other possibilities).

A new Sony patent hints at some ambitious things with the PlayStation 5 and the PS business as a whole. The patent, which was filed in January 2019 and published just days ago, outlines a number of different possibilities. The most exciting one is mention of dual-GPU (or even dual APU) consoles for massively increased performance. Sony could be setting itself up for a PS5 refresh or PS5 Pro with multi-GPU support. This patent isn't that simple, though. There's mention of cloud gaming thrown in the mix so it's not all just based around local hardware.

Before we dive in, I want to remind everyone that this is a patent and not finalized information, meaning nothing's been confirmed or announced. There's no guarantee Sony is actually developing this technology. There's no confirmation that the PS5 Pro is even real or that it will have multiple GPUs, and most importantly, the tech/info outlined herein may not ever be created or released for--or in--a commercially-available system. It's not our intention to mislead anyone, and our interpretations of the patents could be wrong.

From our understanding, this patent has lots of potential for new PlayStation hardware that exceeds the PS5's next-generation capabilities. There's multiple embodiments (or permutations/different ways to present the idea) that outline a number of different methodologies for the tech. And these embodiments are pretty exhaustive.

The most obvious is a PlayStation 5 Pro, but there's also hints that Sony could release a smaller, cheaper PlayStation "stick" with a limited-power APU or SoC chip that's specifically designed for PlayStation Now. The stick would basically be only powerful enough to display and process simple images and the brunt of the image rendering and processing would be done server-side.

First let's dive into the PlayStation 5 Pro possibilities.

PlayStation 5 Pro

The patent kicks things off with an interesting background and summary section that talks about the benefits of using multiple GPUs and linking them together. The summary section explicitly mentions a light version of a console (presumably the base PS5) that could use a single SoC,sand a high-end version (the PS5 Pro) that could use multiple SoCs.

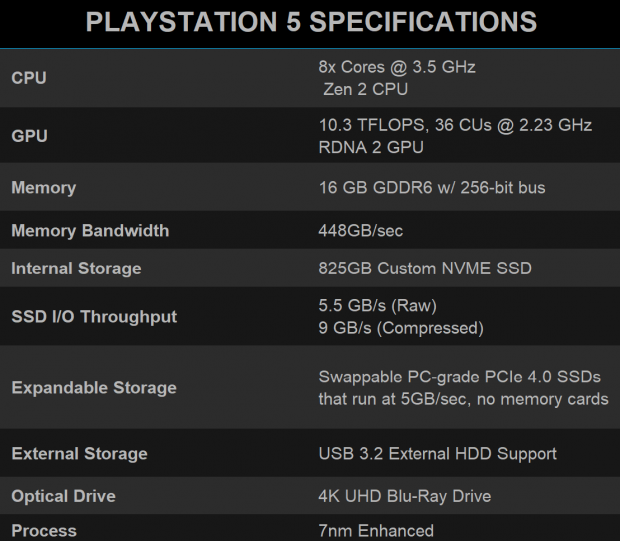

Remember the PlayStation 5 uses a single 7nm SoC from AMD outfitted with a Navi GPU and Zen 2 CPU.

The patent's main goal is to present the possibility of a multi-GPU console with both local and network access to the second GPU. So there's two main ways this could work: A physical console that contains two GPUs, whether it be two SoCs/APUs, or one SoC and a second GPU; or using a GPU from a cloud server network.

The latter is how the PlayStation Now service is powered.

When it comes to physical dual-GPU setups, the patent recognizes there's significant hurdles to tackle such as frame buffer management for rendering. The patent is extremely varied and detailed and aims to cover all the bases for a solution to this problem.

So instead of outlining every single possible solution, we'll give you the gist (we'll also include a full copy of the summary at the bottom of the article for your perusal).

Some of the embodiments have the rendered video split up between the GPUs. One GPU renders one part, the other renders the other part, and the system uses multi-plexing to combine the rendered images and output them to a screen.

FIG. 5 is a block diagram of a shared memory architecture in which two APUs (each including a respective CPU 502 and GPU 504) are shown with each APU being implemented on its own respective die 500 and with a shared memory controller 506 being implemented on one of the dies 500, it being understood that the architecture may be implemented on one die and that more than two APUs may be implemented. The shared memory controller 506 controls access to a memory 508. and the APUs may communicate with each other and with the memory controller 506 over one or more communication paths 510.

The patent also says the console hardware could have two GPUs on a the same die and use the same memory controller and RAM pool, which is uncommon for consoles.

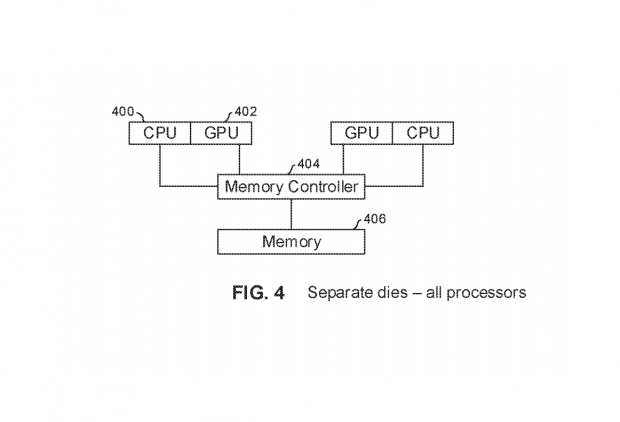

FIG. 4 is a block diagram of a shared memory architecture in which two APUs each including a CPU 400 and GPU 402 are shown with each CPU and each GPU being implemented on its own respective die, it being understood that the architecture may be implemented on fewer or even one die and that more than two APUs may be implemented.

The APUs share a common memory controller 404 that controls a memory 406, and the APUs may communicate with each other and with the memory controller over respective communication paths.

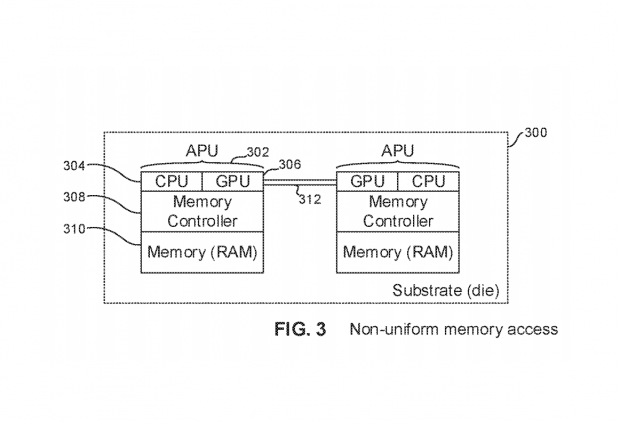

It could also use two separate SoCs with two separate CPUs attached to the same die and using NUMA access, a memory architecture that allows faster access to RAM memory data. The dual SoCs would also have their own RAM pools and memory controllers and would be joined together via a communication bus.

FIG. 3 illustrates an example non-uniform memory access (NUMA) architecture, in which a single fabric 300 holds two APUs 302, 304 on a single die or on respective dies, it being understood that the NUMA architecture may be implemented by more than two APUs. When implemented on respective die chips on the same fabric 300, communication paths, which may be referred to as "busses" for generality, may be established by via layers of the fabric.

As shown, each APU may include one or more CPUs 304 and one or more GPUs 306, typically one CPU and one GPU per APU. Each APU 302 may be associated with its own respective memory controller 308 that controls access to memory 310 such as random-access memory (RAM). Communication between APUs may be affected by one or more communication paths 312, referred to herein for convenience as "busses".

Thus, each APU (or individual GPU) has its own memory controller and hence its own dedicated memory, such as RAM. There can be a (cache-coherent) shared bus between the GPUs, allowing one GPU to access memory of the other GPU.

Theoretically, Sony could make a base PlayStation 5 with a single SoC and a PlayStation 5 Pro with dual SoCs or dual GPU tech for improved power.

This upgraded model would theoretically be better suited for high-end 8K gaming but there's also thermals to consider--the PS5's Navi GPU and PCIe 4.0 could get rather hot, and adding in another GPU could be problematic. But this patent isn't necessarily concerned with thermals.

The patent also mentions how power consumption increases with frequency, and mentions the system will need to fluctuate either power usage or clock frequencies. For reference, the PlayStation 5's redesigned SoC architecture has variable frequency and keeps voltages steady in an effort to reduce fan noise and prioritize heat mitigation.

At the same time, the patent is careful to mention that this extra GPU access could be provided by PlayStation Now servers and not local hardware.

"Similarly, a user may be allocated more dies (and hence more APUs) on a cloud server by paying extra fees, with only a single die being allocated to lower-paying users.

"This may be done when an application starts by programming an API to call for system metrics and spawn threads and determine quality of service based on the metrics. System metrics can be filtered for lower-paying users who are allocated for fewer dies. Higher-paying users desiring the benefit of a multi-threaded game with simultaneous processing can be allocated more dies than lower-paying users."

PS Now server farms could boost console power and increase in-game performance and resolution. Sony could effectively lease access to their beefy servers (which are powered by Microsoft Azure, I might add) similar to NVIDIA's GeForce Now service.

This could be applicable to the PlayStation 5 and even a low-cost digital-only box. Which leads us into our next section.

The $100 PlayStation console "stick"

A few years ago, Microsoft was working on Project Hobart, a streaming-only "stick" that plugged directly into your TV.

The idea is that Hobart would be a mini-console with very minimal power and capabilities. Instead of using an onboard SoC fit for gaming, Hobart would borrow power form Microsoft's mighty cloud server banks. The hardware was abandoned because didn't have a game streaming infrastructure (it does now, and it's called Project xCloud).

But Sony has its PlayStation Now service, and this patent could see the service pumping out serious gaming power to low-cost boxes or even streaming sticks for massively-accessible gaming.

By mimicking Project Hobart, Sony could effectively launch the cheapest PlayStation console ever. It'd be a small, low-power box or HDMI stick that plugs right into a TV and leverages PlayStation Now servers for game performance and streaming. Sony could outfit its PS Now servers with PlayStation 5 consoles to deliver PS5-esque performance to these boxes over the cloud.

This could also allow Sony to natively add PlayStation gaming to its line of premium Bravia TVs. These UHDTVs could be equipped with these boxes and directly connect to PlayStation Now to allow built-in PS4 and PS5 cloud gaming.

An older Sony patent also seems applicable here. In it, Sony outlined how the PlayStation 5's DualSense controller could connect directly to the PlayStation Now network without needing a console. This would let consumers connect their next-gen Dualsense controllers directly to the low-cost box (or even the aforementioned console-free Bravia TVs) for cloud gaming.

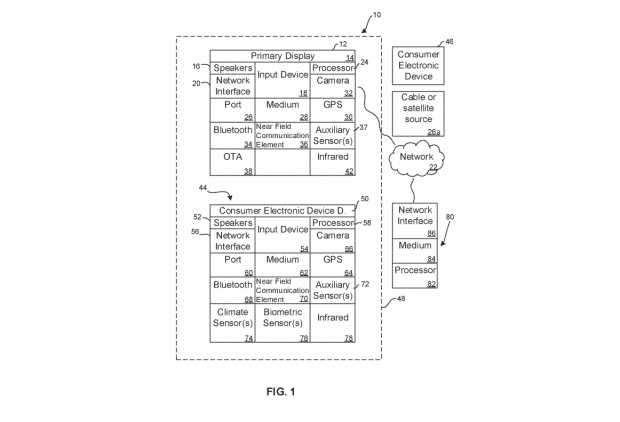

Accordingly, in some embodiments the server 80 may be an Internet server or an entire "server farm" and may include and perform "cloud" functions such that the devices of the system 10 may access a "cloud" environment via the server 80 in example embodiments for, e.g., network gaming applications. Or, the server 80 may be implemented by one or more game consoles or other computers in the same room as the other devices shown in FIG. 1 or nearby.

Wrap-Up

As we said before, remember that this is a patent. There's no concrete evidence Sony is making a PS5 Pro with multiple GPUs. There's lots of issues with a dual-SoC or -APU system to consider and we'll probably see more patents pertaining to this in the near future.

But for now, we at least know Sony is trying to cover its bases and future-proof its plans for the PlayStation brand. There's no telling what'll come of this patent though.

The PlayStation 5 is due out Holiday 2020. No pricing has been announced.

Check below for full specs of the PS5, alongside a full background/summary of the covered patent:

BACKGROUND

Simulation consoles such as computer game consoles typically use a single chip, referred to as a "system on a chip" (SoC) that contains a central processing unit (CPU) and a graphics processing unit (GPU). Due to semiconductor scaling challenges and yield issues, multiple small chips can be linked by high-speed coherent busses to form big chips. While such a scaling solution is slightly less optimal in performance compared to building a huge monolithic chip, it is less costly.

SUMMARY

As understood herein. SoC technology can be applied to video simulation consoles such as game consoles, and in particular a single SoC may be provided for a "light" version of the console while plural SoCs may be used to provide a "high-end" version of the console with greater processing and storage capability than the "light" version. The "high-end" system can also contain more memory such as random-access memory (RAM) and other features and may also be used for a cloud-optimized version using the same game console chip with more performance.

As further understood herein, however, such a "high-end" multiple SoC design poses challenges to the software and simulation (game) design, which must scale accordingly. As an example, challenges arise related to non-uniform memory access (NUMA) and thread management, as well as providing hints to software to use the hardware in the best way. In the case of GPUs working in concert, the framebuffer management and control of high definition multimedia (HDMI) output may be addressed. Other challenges as well may be addressed herein.

Accordingly, an apparatus includes at least a first graphics processing unit (GPU), and at least a second GPU communicatively coupled to the first GPU. The GPUs are programmed to render respective portions of video, such that the first GPU renders first portions of video and the second GPU renders second portions of the video, with the first and second portions being different from each other.

Stated differently, the first GPU may be programmed for rendering first frames of video to provide a first output, while the second GPU is programmed rendering some, but not all, frames of the video to provide a second output.

The frames rendered by the second GPU are different from the frames rendered by the first GPU. The first and second outputs may be combined to render the video.

In addition, or alternatively, the first GPU may be programmed for rendering all of some, but not all, lines of a frame of video to provide a first line output and the second GPU may be programmed for rendering some, but not all, lines of the frame of the video to provide a second line output. The lines rendered by the second GPU are different from the lines rendered by the first GPU. The first- and second-line outputs can be combined to render the frame.

In some embodiments, the first and second GPUs are implemented on a common die. In other embodiments, the first and second GPUs are implemented on respective first and second dies. The first GPU may be associated with a first central processing unit (CPU) and the second GPU may be associated with a second CPU.

In some implementations, a first memory controller and first memory are associated with the first GPU and a second memory controller and second memory are associated with the second GPU. In other implementations, the GPUs share a common memory controller controlling a common memory.

In some examples, each GPU is programmed to render all of some, but not all, frames of video different from frames of the video rendered by the other GPU to provide a respective output. The outputs of the GPUs can be combined to render the video. In other examples, each GPU is programmed to render all of some, but not all, lines of a frame of video, with lines of a frame of video rendered by a GPU being different from lines of the frame rendered by the other GPU to provide a respective output. The outputs of the GPUs can be combined to render the video.

In an example technique, the first GPU includes at least one scanout unit pointing to at least one buffer managed by the second GPU. The first GPU can be programmed to cycle through buffers to output a complete sequence of frames of the video. In another example, the first GPU includes at least one scanout unit pointing only to buffers managed by the first GPU and is programmed to receive frames of the video from the second GPU via direct memory access (DMA) to output a complete sequence of frames of the video.

In yet another example technique, the first GPU includes at least one scanout unit pointing to at least a first buffer managed by the first GPU and a second buffer managed by the second GPU. In this technique, the first GPU is programmed to cycle through buffers to output a complete sequence of frame of video using 1-N lines associated with the first buffer and (N+1)-M lines associated with the second buffer. The 1-N lines are different lines of the same frame associated with the (N+)-M lines.

Yet again, the first GPU can include at least one scanout unit pointing to at least a first buffer managed by the first GPU and not to a second buffer managed by the second GPU. In this implementation, the first GPU may be programmed to cycle through buffers to output a complete sequence of frame of video using 1-N lines associated with the first buffer and (N+1)-M lines associated with the second buffer and received by the first GPU via direct memory access (DMA). The 1-N lines and (N+1)-M lines are different lines of the frame of video.

In still another technique, the first GPU includes at least one scanout unit pointing to at least a first buffer communicating with the common memory controller. The second GPU includes a second buffer communicating with the common memory controller. The first GPU is programmed for rendering 1-N lines associated with the first buffer and the second GPU is programmed for rendering (N+1)-M lines associated with the second buffer.

In some examples, the first GPU manages video data output from the first and second GPUs. This may be affected by physically connecting a HDMI port to the first GPU. In other examples, the GPUs output video data to a multiplexer that multiplexes the frames and/or lines from the respective GPUs together to output video.

In another aspect, in a multi-graphics processing unit (GPU) simulation environment, a method includes causing plural GPUs to render respective frames of video, or to render respective portions of each frame of video, or both to render respective frames and respective portions of frames of video. The method includes controlling frame output using a first one of the GPUs receiving frame information from at least one other of the GPU(s), or multiplexing outputs of the GPUs together, or both using a first one of the GPUs receiving frame information from at least one other of the GPU(s) and multiplexing outputs of the GPUs together.

In another aspect, a computer simulation apparatus includes at least a first graphics processing unit (GPU) programmed for rendering a respective first portion of simulation video, and at least a second GPU programmed for rendering a respective second portion of simulation video. At least the first GPU is programmed to combine the first and second portions and to render an output establishing a complete simulation video.