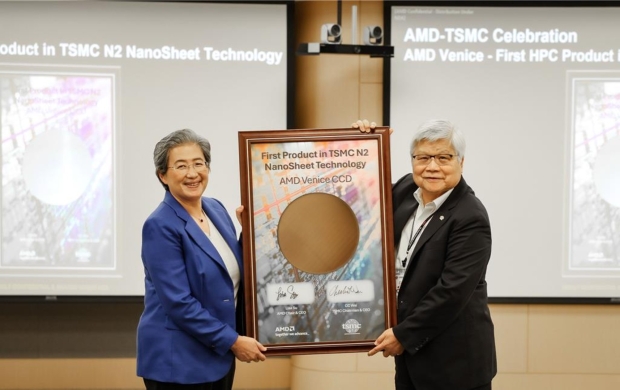

AMD has just announced that its next-gen EPYC processor codenamed "Venice" is the first HPC product in the industry to be taped out and brought up on TSMC's advanced 2nm (N2) process technology.

This announcement highlights the strength of AMD and TSMC semiconductor manufacturing partnership to co-optimize new design architectures with leading-edge process technology, with the stars of the show here being the new EPYC "Venice" CPU and 2nm (N2) process node tech.

AMD says that this news also marks a major step forward in the execution of the successful bring up and validation of its 5th Gen AMD EPYC CPU products at TSMC's new fabrication facility in Arizona, Texas, with the company adding "underscoring its commitment to US manufacturing".

Dr. Lisa Su, chair and CEO, AMD, said: "TSMC has been a key partner for many years and our deep collaboration with their R&D and manufacturing teams has enabled AMD to consistently deliver leadership products that push the limits of high-performance computing. Being a lead HPC customer for TSMC's N2 process and for TSMC Arizona Fab 21 are great examples of how we are working closely together to drive innovation and deliver the advanced technologies that will power the future of computing".

TSMC Chairman and CEO Dr. C.C. Wei, added: "We are proud to have AMD be a lead HPC customer for our advanced 2nm (N2) process technology and TSMC Arizona fab. By working together, we are driving significant technology scaling resulting in better performance, power efficiency and yields for high-performance silicon. We look forward to continuing to work closely with AMD to enable the next era of computing".