Intel is finally preparing to take on AMD's awesome X3D cache on its CPUs with next-gen Core Ultra 400K series "Nova Lake-S" desktop CPUs reportedly featuring 144MB of bLLC (big cache) as an answer to 3D V-Cache (X3D) on Ryzen X3D series CPUs.

The latest reports suggest that Intel will only include its bLLC cache on the next-gen Core Ultra 400K unlocked SKUs, while AMD still offers X3D cache across a far wider range of Ryzen CPUs. In a new post from leaker @Jaykihn, who says that the Core Ultra 400K series will feature 144MB of bLLC (Big Last Level Cache).

AMD has been using its X3D cache on mid-range Ryzen CPUs which cost under $500, to beat out much more expensive flagship CPUs from Intel without any pool of cache, meaning gamers could buy a far cheaper CPU and still have commanding gaming performance thanks to the X3D cache.

Secondly, bundle the cheaper mid-range Ryzen 5000X3D or 7000X3D processor with a mid-range AM5 motherboard and you've got a cheaper system than a higher-end Intel system which costs significantly more (and requires more cooling for a high-end Intel CPU which chews down on power and creates considerable heat compared to a mid-range Ryzen CPU from AMD).

Intel will finally catch up to AMD with its next-gen Core Ultra 400K series "Nova Lake-S" desktop processors with its purported bLLC cache on its unlocked processors, but AMD is rumored to come out swinging at CES 2026 with the unveiling of its Ryzen 9 9950X3D2 and Ryzen 7 9850X3D processors with dual X3D cache with a total of 192MB of L3 cache, higher CPU clock speeds, and higher TDPs for more power.

AMD's purported Ryzen 9 9950X3D2 processor would roll-out as a mega version of the current Ryzen 9 9950X3D2 (that "2" is important) as it'll feature the same 16 cores and 32 threads of Zen 5 processing power, but a larger chunk -- double -- the X3D CCD cache, with a total of 192MB cache. The new 9950X3D2 is also poised to feature a higher 200W TDP, so we should expect some mega overclocks from the new chip when it's released.

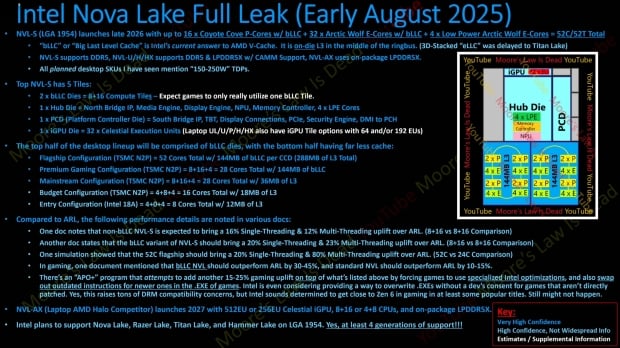

On the Intel side, there are reportedly five Tiles on Nova Lake-S, with 2 x bLLC dies = 8+16 Compute Tiles, with MLID noting that we should expect games to only really utilize one bLLC Tile. We should expect the flagship Nova Lake-S processor to be made on TSMC's bleeding-edge N2P process node, with 52 cores + 144MB of bLLC per CCD for a huge 288MB of L3 cache in total.