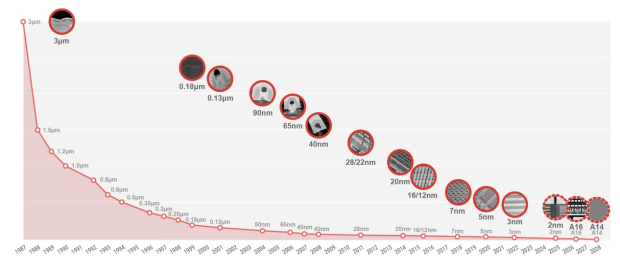

TSMC is making great strides in the development of its next-gen A16 and A14 process node technology, with huge improvements over its N2 process node in both performance and energy efficiency.

In a new post on X by Research Director and Semiconductor Analyst at The Futurum Group, Ray Wang, that TSMC says its next-gen A14 node (1.4nm) has achieved "yield performance" ahead of schedule. The performance improvements expected from TSMC's next-gen A14 node are impressive to say the least.

TSMC's upcoming A16 technology will integrate nanosheet transistors with Super Power Rail (SPR) and novel backside contacts to deliver industry-leading logic density, power efficiency, and most importantly: performance. A16 compared to N2 will see 8-10% higher speed, 15-20% less power, and around 1.1x chip density, making TSMC's upcoming A16 process perfect for HPC products that need complex signal routing and robust power delivery.

A14 on the other hand is a full-node scaling successor to N2, made for AI and smartphone chips with improved NanoFlex Pro cell architecture. When compared against N2, TSMC's next-gen A14 process node provides 15% more speed, up to 30% lower power, and over 20% density gain, which translates into faster compute, greater efficiency, and enhanced on-device AI performance.

TSMC says "A14 development is progressing smoothly with yield performance ahead of schedule". We can expect big tech companies like Apple, NVIDIA, AMD, and others that will adopt TSMC's upcoming A16 and A14 process nodes, with TSMC looking for a 2028 production for its new A14 technology.