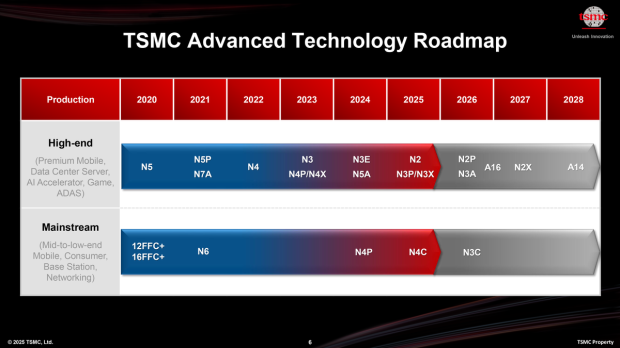

TSMC says that it remains on track to begin high-volume production of next-gen chips on its new N2 (2nm-class) process node, the first production tech that uses gate-all-around (GAA) nanosheet transistors, in the second half of this year.

The news was unveiled during TSMC's recent North American Technology Symposium 2025 event, with its new N2 node to power multiple products this year from AMD, Apple, and most recently, Intel.

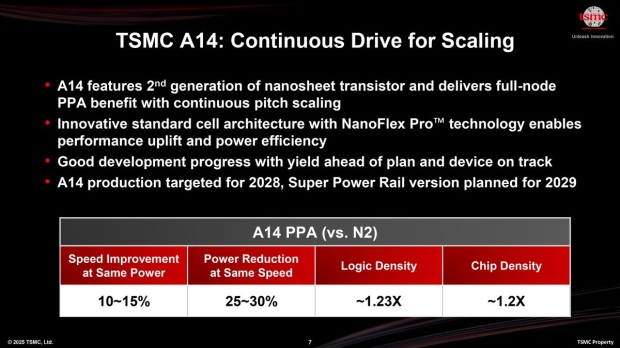

TSMC's next-gen A14 process node, when compared against the upcoming N2 process, will have 15% more performance using the same power, or up to 30% power reduction at the same speed, along with over 20% more logic density. TSMC will be evolving its NanoFlex standard cell architecture to NanoFlex Pro, enabling greater performance, power efficiency, and design flexibility.

Not only can we expect TSMC's ultra-bleeding-edge N2 process node in 2028, but the Taiwanese semiconductor leader also debuted new logic, specialty, advanced packaging and 3D chip stacking technologies, all of which contribute to broad technology platforms in high-performance computing (HPC), smartphone, automotive, and Internet of Things (IoT) says TSMC.

TSMC Chairman and CEO Dr. C.C. Wei said: "Our customers constantly look to the future, and TSMC's technology leadership and manufacturing excellence provides them with a dependable roadmap for their innovations. TSMC's cutting-edge logic technologies like A14 are part of a comprehensive suite of solutions that connect the physical and digital worlds to unleash our customers' innovation for advancing the AI future".

Kevin Zhang, senior vice president of business development and global sales and deputy COO at TSMC, said: "A14 is our full-node next generation advanced silicon technology. If you look at speed, enhancement [compared to N2] is up to 15%, power reduction is at 30%, logic density is 1.23x the overall chip density, or at least 1.2x [for mixed designs]. So, this is a very, very substantial technology".

Zhang added: "The technology also features our [...] NanoFlex Pro technology, [which is really] design technology co-optimization (DTCO) allowing designer to design their product at a very flexible fashion, allow them to achieve optimum power performance benefit. This technology is going into production by 2028. The first version of this technology does not have the backside power rail".