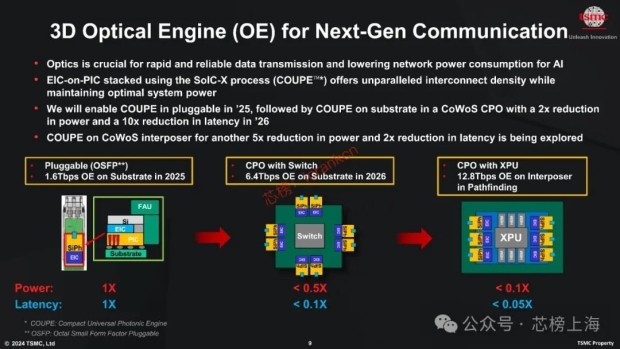

TSMC's next-gen silicon photonics advancements are hitting new strides, with its first co-packaged optics (CPO) samples expected to reach NVIDIA and Broadcom in 2025, pushing speeds of up to 1.6 terabits-per-second (1.6T) over fiber optic connections inside of new AI data centers in 2H 2025.

TSMC and Broadcom have jointly developed microring modulator (MRM) which has recently passed 3nm trial production, paving the way of integrating of top AI chips into CPO modules, with TSMC expected to use its CoWoS or SoIC advanced packaging.

In a new report from UDN, we're learning that the new advanced semiconductor packaging technology allows for 1.6T optical transmission, with NVIDIA and Broadcom being the first two customers of TSMC's latest tech. One of the leads on the silicon photonics packaging technology is the co-CEO of TSMC, Chiang Shangyi, who has industry-leading capabilities in optical communication components and semiconductor chip packaging technology, and works closely with Broadcom.

Industry analysts point out that TSMC's current silicon photonics technology concept is mainly to integrate CPO modules with advanced packaging technologies like CoWoS or SoIC, so that transmission signals aren't limited by the speeds of traditional copper lines. 1.6T is expected to enter mass production in 2H 2025 at the earliest, shipping sometime in 2026.

NVIDIA will have its "market-grabbing" weapon unveiled at GTC 2025 in March, with the new GB300 AI servers expected to feature optical module upgrades from 800G to 1.6T, so expect more news from TSMC, NVIDIA, and Broadcom about this exciting development in silicon photonics