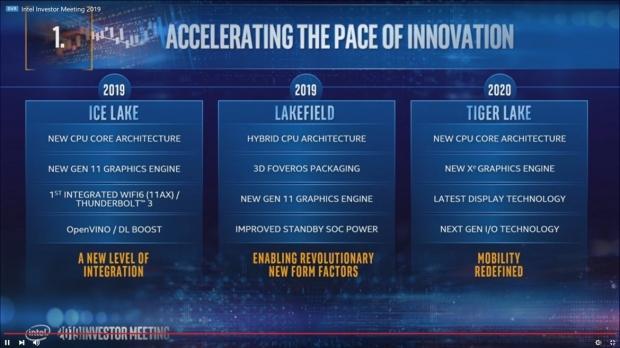

Intel is expected to launch its next-gen Tiger Lake CPU architecture sometime in late 2020 or 2021, which will feature Gen12 graphics and a total overhaul of the Execution Unit.

The revamped Execution Unit is expected to provide the largest GPU performance increase in over 10 years, something that was revealed in a new release of Linux patches from Intel. The post talks about a new Display State Buffer (DBS) engine that will take care of batch submit display register programming.

The documentation states that DBS reduces "loading time and CPU activity, thereby making the context switch faster. DSB Support added from Gen12 Intel graphics based platform".

- Read more: Intel Nova Lake CPUs rumored to feature hybrid Xe3 & Xe3P architectures, no sign of Xe4 'Druid' for now

- Read more: Sony explains how it modified PS5 Pro's GPU to enable PSSR neural network AI upscaling

- Read more: AMD look out, NVIDIA and Intel's new chips will target laptops and PC gaming handhelds

Intel has teased it is making "the most in-depth" EU ISA remake since its i965 processor that arrived over 10 years ago now, with Francisco Jerez who is part of the open-source Linux graphics team at Intel, explained: "The encoding of almost every instruction field, hardware opcode and register type needs to be updated in this merge request".

He continued: "But probably the most invasive change is the removal of the register scoreboard logic from the hardware, which means that the EU will no longer guarantee data coherency between register reads and writes, and will require the compiler to synchronize dependent instructions anytime there is a potential data hazard".

Intel's next-gen Gen12 graphics will be the first to market powered by the first-gen Intel Xe GPU architecture, which will be the GPU architecture that will power Intel's first discrete graphics card launching in 2020.