We've all seen HBM deployed on various GPU's primarily from AMD starting back in the days of the FURY and FURY X. However the market for HBM has grown quite a lot and is used for not just GPU but similar devices such as compute accelerators and FPGAs

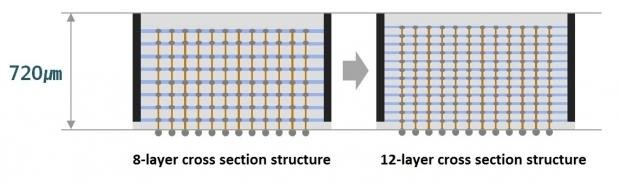

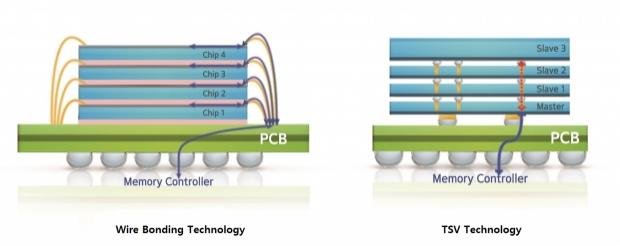

Samsung today announced that they have developed an industry first in the new 12-layer 3D-TSV (Through Silicon Via) design. The design uses 60,000 TSV holes to enable the stacking of DRAM chips in a vertical configuration. The TSV holes are stated to be one-twentieth the thickness of a human hair.

This new tech can allow for the new stacking of 12 DRAM chips through these holes on much thinner slices allowing the package to occupy the same 720micron thickness. This means that theoretically, an existing design using 8-layer tech can now equip up to 48GB or even up to 96GB of HBM dependent upon bus width. In the case stated above, that would be 2048-bit or 4096-bit, but this could also mean refinement for lower density packages for applications not requiring high density such as consumer GPUs.

We know that GDDR6 is all the rage today on current consumer GPUs, but with this tech, if the BOM is favorable can mean some serious memory capabilities on future flagship GPUs.