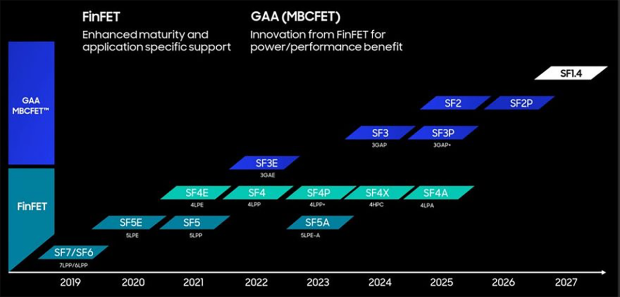

Samsung Foundry will be using its new SF2 (2nm-class) manufacturing process as its first with a backside power delivery network (BSPDN), according to the latest reports.

Chosun.com is reporting that the promising results that were achieved by using backside power delivery changed Samsung's thoughts on the technology, seeing the company rethink the use of BSPDN into a commercial process technology. Samsung was expected to introduce a backside power delivery network with its 1.7nm-class fabrication node, but it will arrive with its SF2 process node in 2025.

As Tom's Hardware points out: there is no 1.7nm-class nodes on Samsung's current roadmaps, where we can only see SF2, SF2P, and SF1.4 process nodes. Samsung has used two Arm-based test chips with backside power delivery, achieving a 10% and 19% die area reduction without telling the world which process node it's using.

- Read more: Intel unveils new Intel 14A process node, ready for future AI chip production

- Read more: Analyst: TSMC the world's biggest semiconductor maker by revenue

- Read more: Samsung wants to beat TSMC in 3nm manufacturing, 2nm coming in 2025

- Read more: Samsung to invest $151 billion into chip manufacturing through to 2030

Backside power delivery allows for thicker, lower-resistence wires, which are capable of delivering more power, and thus more performance, with less power used. Samsung's research paper saw that backside power delivery has benefits like a 3.6% Fmax improvement, a 2.4% standard block area reduction, and 1.6% standard block performance improvement.

Samsung getting backside power delivery into its upcoming SF2 process technology seems like a reaction to Intel's advancements with its Intel 20A and Intel 18A fabrication technology coming in 2025, and TSMC's upcoming N2P process that rolls off fabrication plant lines in 2026-2027.