Introduction

Could it finally be Intel's day to shine?

For over 6 years now, Intel has put all of its research and money behind its Pentium line of CPU's and until the last 3 yeas, it has been an up and down ride taking on the new CPU giant AMD, who's Athlon series of processors has partly been the bane of Intel's existence.

K7 and K8 architectures was something Intel probably wished never saw the light of day, especially when it came to Pentium 4's somewhat weaker architecture. All of Intel's processors since the Pentium 4 were introduced using the Netburst Micro Architecture. This architecture was designed for speed, raw CPU MHz. Its extremely long pipeline and twin double speed ALU's allowed speeds hitting 3.8GHz and if things continued, maybe more. Only problem is, clock for clock. AMD's K8 architecture managed to destroy the Pentium 4 architecture, and power per watt, AMD's CPU are like an arctic winter compared to the Netburst CPU's especially the Prescott and Presler based units.

Today marks a big change for Intel. It's the first time since the early 90's that its new top market CPU has not carried the Pentium logo - in fact, Pentium branding is now set to die a slow death with the Pentium D to be the last CPU's from Intel to continue production for a few more month, then we will see only new processors based on Intel's latest architecture, named "Core Architecture"

So far Intel has already released one CPU series based on this new architecture. Core Duo and Core Solo for the mobile sectors have already emerged; today we are looking at Core 2 series for the desktop section. In our labs we have Intel's twin Core 2 components, the Core 2 Extreme (X6800) and the Core 2 Duo (E6700).

Core vs. Netburst

Core Architecture in detail

The Core Architecture is now a step away from Intel's future proof Netburst architecture in quite a few ways. In fast it's almost totally redesigned, only using the same FSB and electrical connections to make it compatible with Socket 775 and existing Pentium 4 supporting chipsets like the Intel 975X, this is where things end in similarities.

Intel's Core Architecture includes a few new technologies that distinguish it from the previous generation CPU. Multi Platform Architecture, Wide Dynamic Execution, Intelligent Power Capability, Advanced Smart Cache, Smart Memory Access and Advanced Digital Media Boost to name just a few. So let's have a look at a few of these features and try to explain them as best as possible without needing a degree in rocket science.

- Multi Platform Architecture

Intel's Core Architecture is a first for Intel's platform development. Core Architecture has been designed to support not only the desktop environment but also mobile and servers. With different array of power saving features, cache sizes and bus implementations, core based CPU's can be tailored for each platform. Benefits of this style of architecture means there is no added costs in researching a separate CPU platform architecture to run servers, desktops and notebooks, using a single architecture that can be tailored during production allows a cheaper CPU and platform cost to the consumer.

- Intel Wide Dynamic Execution

Wide Dynamic Execution is just a fancy way for Intel to say it has widened the execution path of core CPU's. Rather than 3 execution pipes, core CPU's have 4. This allows the Core Architecture to process 4 simultaneous instructions per clock cycle. This reduces the amount of clock cycles needed to execute a program, reducing power consumption as the CPU is at load for less time. With Wide Dynamic Execution comes another feature built into the pipeline called "Macro Fusion". When the instructions are loaded into the decoder, if a common pair of instructions are found in the decode buffer, Macro combines the 2 and sends them down to the Execution stage in a single packet. This doubles the data that is sent allowing 2 instructions to be sent simultaneously. Increasing the amount of data processed per clock cycle.

- Intel Intelligent Power Gating

Intelligent Power Gating is further work by Intel on its SpeedStep technologies, only taken up a notch. When the CPU isn't required to run at 100% load, previous CPU's like the Pentium 4 and even the AMD Athlon 64 still turn on the full amount of execution pipes and so on. Intelligent Power Gating determines how much CPU resources are needed and only turns on what is needed and leaves the rest in an idle state. This allows certain areas of the CPU to remain idle while others are operating. If more are needed, the CPU will open up the extra gates and bring the CPU up out of idle state without the user noticing any performance hit. This technology is especially useful for the mobile sector allowing for a greater battery life as well as desktop and small form factor PC's reducing the amount of power and heat generated per clock cycle.

- Smart Cache Technology

Smart Cache is Intel's latest way of not only reducing the amount of cache memory needed for its dual core CPU's but also a way to increase the efficiency of the data being shared between the 2 cores. Traditionally in dual core CPU's you have 2 separate CPU's with their own L1 and L2 caches fused together on a single die and using either the FSB for core to core communication like in the Pentium D or Pentium Extreme Edition CPU's from Intel or a Crossbar interface such as the AMD Athlon 64 X2's. Smart Cache works differently in that both cores have a separate L1 cache but share a common L2 cache.

This cache is dynamic allocation and power saving. Dynamic allocation means that which ever core needs the most amount of L2 cache, then that core gets the most amount. If both need the same amount, the cache is split down the middle for each core. This also reduces latency between core to core communication as both cores can access the same data in L2 cache at the same time allowing each core to know what each other is doing rather than having to come across the FSB and into main memory like the previous Pentium D/XE range of CPU. This also reduces cache misses in that if core 1 requires some data from the L2 cache it is loaded into the common cache, in traditional dual core, this data may be in core 2's L2 cache, resulting in a cache miss and requiring the L2 cache of core 1 to access the data from main memory while core 2's L2 cache needs to be cleared of this data.

The power saving feature is derived from the Pentium-M series CPU. When the CPU enters the idle state, half of the cache is dynamically turned off and put into a deep state of hibernation until it is needed, further reducing the amount of power consumed by the CPU when under idle states.

- Smart Memory Access

Intel's Smart Memory Access includes a new technology called memory disambiguation. With this new feature each core is able to guess what data is needed from memory and is able to retrieve it before all the previous instructions in the queue have been completed. This allows for reduced memory latency as well as a much simpler memory allocation system. Should the data received be the wrong packet, the instruction is sent back to the execution engine to await the right data, which prevents stalls and wait states.

- Digital Media Boots

This is by far one of the more interesting features of the Core Architecture. Streaming SIMD instructions are 128-bit codes put together in packages, for Intel they are SSE, SSE2 and SSE3. Previous CPU's to execute these had to be broken down into 64-bit instructions, so for a Netburst based CPU to execute a single SIMD Instruction it would take 2 clock cycles, 1 cycle to execute the top 64-bits and a second cycle for the lower 64-bit. With the new deeper execution buffers in the new Core architecture CPU's, the execution engine can process a single 128-bit instruction in just 1 clock cycle. This is particularly useful when graphical media and content creation is involved as well as encoding of audio and video media.

Core 2 Duo - Tailored for the Desktop

Core 2 up close

Now we have gone over the features of the Core Architecture, it's time to take a look at the desktop version CPU's known as Core 2 Duo and Core 2 Extreme Edition.

Intel's Core 2 series CPU in fact look almost identical to the Pentium 4, Pentium-D and Pentium Extreme Edition CPU's. This is because they are designed to work in the exact same Socket T or LGA775 sockets. Intel has approved the 975X chipset along with its new P965 chipset for use with Core 2 CPU's.

From the bottom you see that the same LGA775 pinless design is used, in fact it's hard to tell the difference between all 3 cores. Let's start off with the pricing first:

As we mentioned in our early benchmark preview from Taiwan during Computex, Intel will have a complete set of Core 2 series CPU's designated with a new 4 digit naming series. Today we have the Core 2 Extreme X6800 and the Core 2 Duo E6700 in our labs. In the range Intel has for launch there will be only a single Extreme Edition model, the X6800 and in the Core 2 Duo there is E6700 and E6600. These 3 cores will operate with a 1066MHz FSB (266 Quad Pumped) with a 4MB Smart Cache, EM64T and Executable Bit.

In the lower end of things the Core 2 Duo will come out in E6300 and E6400. These parts will only have a 2MB Smart Cache but will still include EM64T, 1066FSB and XD Bit. On the value end the Core 2 Duo E4200 will come out only with 2MB Smart Cache and run at 800MHz FSB. There is no EM64T or XD Bit, possibly the Celeron version of the Core 2 line? All current Core 2 CPU's have no Hyper Threading enabled; we aren't sure if they even have it built into the core. Intel may decide to release a new series down the line with HT technology, but this is not been confirmed as yet.

The motherboard Intel supplied to us for testing is a revised version of the 975X reference board they sent us when we first tested the 975X series chipset. This is because of the lack of P965 boards currently available, even Intel doesn't have its own P965 board ready yet for the masses.

Benchmarks - Test Systems and Sisoft Sandra

Intel Test System

Processor: Intel Pentium Extreme Edition 955, Intel Pentium-D 940 and Intel Core 2 CPU's (Supplied by Intel)

Motherboard: Intel 975XBX Reference

Memory: 2x 1GB DDR2-1000 Corsair

Hard Disk: Seagate 7200.9 500GB (Supplied by Seagate)

Graphics Card: nVidia GeForce 7800GT

Operating System: Microsoft Windows XP Professional SP2

Drivers: Intel INF 8.0.1.1002 and nVidia ForceWare 91.31

AMD K8 Test System

Processor: AMD Athlon 64 X2 3800+ AM2 @ 2.6GHz (260MHz x 10)

Motherboard: MSI K9N Platinum

Memory: 2x 1GB DDR2-1000 Corsair

Hard Disk: Seagate 7200.9 500GB (Supplied by Seagate Australia)

Graphics Card: nVidia GeForce 7800GT

Operating System: Microsoft Windows XP Professional SP2

Drivers: nVidia ForceWare 91.31 and nForce 570 9.1

This time around since the Intel 975XBX supports all of the processors we want to use we have chosen this board as our Intel test platform. Luckily we have an AMD Athlon 64 X2 on the AM2 platform and a supporting motherboard, so this is what we have chosen to run against.

We don't have an FX-60 or FX-62 because AMD doesn't have enough processors to send to all media around the world. Instead we had to make do and take a 3800+ and overclock it to 2.6GHz (260MHz x 10). In theory, this turns out 3800+ CPU into something like a 5000+ CPU.

We've benchmarked the Core architecture before but this time we test in our own labs and have more time with the processors. Is it Intel's day to shine and take back the CPU performance crown from AMD? Let's find out now!

SiSoft Sandra

Version and / or Patch Used: 2007

Developer Homepage: http://www.sisoftware.co.uk

Product Homepage: http://sisoftware.jaggedonline.com/index.php?location=home&a=TTA&lang=en

Buy It Here

SiSoft Sandra (System ANalyser, Diagnostic and Reporting Assistant) is a synthetic Windows benchmark that features different tests used to evaluate different PC subsystems.

In our CPU raw performance benchmark we see that the Core 2 does fall behind Netburst's raw FPU and ALU results - this is likely because of the double speed ALU's that this CPU incorporates.

Memory wise its up on the mark against the Netburst but falls back on AMD due to a on die memory controller used by AMD. Intel still relied on the chipset to support its memory controllers and requires the FSB for CPU to memory communication.

Benchmarks - PCMark

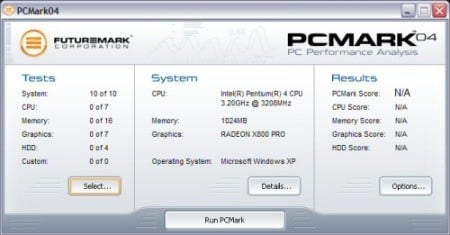

PCMark

Version and / or Patch Used: 1.1.0

Developer Homepage: http://www.futuremark.com

Product Homepage: http://www.futuremark.com/products/pcmark04/

Buy It Here

PCMark is a multipurpose benchmark, suited for benchmarking all kinds of PCs, from laptops to workstations, as well as across multiple Windows operating systems. This easy-to-use benchmark makes professional strength benchmarking software available even to novice users. PCMark consists of a series of tests that represent common tasks in home and office programs. PCMark also covers many additional areas outside the scope of other MadOnion.com benchmarks.

PCMark puts Core 2 ahead of AMD on the CPU front, but again lacks in memory performance. The overall result though favours Core 2.

Benchmarks - Super PI

Super PI

Version and / or Patch Used: 1.1e

Developer Homepage: http://pw1.netcom.com/~hjsmith/Pi/Super_Pi.html

Product Homepage: http://pw1.netcom.com/~hjsmith/Pi/Super_Pi.html

Developed by some folks from the University of Tokyo (yes, Japan), Super PI is a small utility that does just as the name implies. It figures PI to a set number of decimal places. Since PI is an infinite number to the right of the decimal point, the utility measures the time it takes to figure a set number of places. It runs the calculations a set number of times and gives a time for the completion of the task. This is a simple and effective way to measure the raw number crunching power of the processor being used to compile the results.

Pure Mathematical calculations are just what the Core 2 loves to get its mitts into and manages to simply kill the K8 and Netburst based processors.

Benchmarks - Media Encoding

MPEG2 to DivX Encoding with Power Director

Version and / or Patch Used: 5.0

Developer Homepage: http://www.cyberlink.com

Product Homepage: http://www.cyberlink.com/multi/products/main_4_ENU.html

Buy It Here

CyberLink Power Director produces video files for creating DVD, DivX, XviD and WMV files for use on your PC. Using the built in software we encode files from MPEG2 (DVD) format to DivX format and use the time taken, average FPS and CPU usage for our benchmarking usage.

With the new and improved Digital Media Boost video encoding times are cut down impressively while still keeping a good frame rate and a low CPU usage.

Benchmarks - 3DMark05

3DMark05

Version and / or Patch Used: Build 120

Developer Homepage: http://www.futuremark.com

Product Homepage: http://www.futuremark.com/products/3dmark05/

Buy It Here

3DMark05 is now the second latest version in the popular 3DMark "Gamers Benchmark" series. It includes a complete set of DX9 benchmarks which tests Shader Model 2.0 and above.

For more information on the 3DMark05 benchmark, we recommend you read our preview here.

3DMark05 is our first gaming benchmark, though synthetic, it puts the Core 2 CPU's ahead of the rest.

Benchmarks - 3DMark06

3DMark06

Version and / or Patch Used: Build 102

Developer Homepage: http://www.futuremark.com

Product Homepage: http://www.futuremark.com/products/3dmark06/

Buy It Here

3DMark06 is the very latest version of the "Gamers Benchmark" from FutureMark. The newest version of 3DMark expands on the tests in 3DMark05 by adding graphical effects using Shader Model 3.0 and HDR (High Dynamic Range lighting) which will push even the best DX9 graphics cards to the extremes.

3DMark06 also focuses on not just the GPU but the CPU using the AGEIA PhysX software physics library to effectively test single and Dual Core processors.

Again we see a similar trend to 3DMark05.

Benchmarks - Doom 3

Doom 3

Version and / or Patch Used: 1.1

Timedemo or Level Used: Custom Timedemo

Developer Homepage: http://www.idsoftware.com

Product Homepage: http://www.doom3.com

Buy It Here

Doom 3 is still one of the most popular games at the moment and is quite intensive in the 3D department, even though it is starting to age. With our own custom time demo we are able to give a realistic rating on what kind of FPS you will be achieving.

For more information on benchmarking Doom 3 we recommend you check out our extensive article regarding it here.

In our first real world benchmark Intel Core 2 manages to stay ahead of the Netburst and K8 architectures.

Benchmarks - Quake 4

Quake 4

Version and / or Patch Used: Unpatched

Timedemo or Level Used: Custom Timedemo

Developer Homepage: http://www.idsoftware.com

Product Homepage: http://www.quake4game.com

Buy It Here

Quake 4 is one of the latest new games to be added to our benchmark suite. It is based off the popular Doom 3 engine and as a result uses many of the features seen in Doom. However, Quake 4 graphics are more intensive than Doom 3 and should put more strain on different parts of the system.

Quake 4 shows similar trends as Doom 3 since they are both based off the same game engine.

Benchmarks - F.E.A.R.

F.E.A.R.

Version and / or Patch Used: Unpatched

Timedemo or Level Used: Custom Timedemo

Developer Homepage: http://www.vugames.com

Product Homepage: http://www.whatisfear.com/us/

Buy It Here

F.E.A.R. (First Encounter Assault Recon) is an intense combat experience with rich atmosphere and a deeply intense paranormal storyline presented entirely in first person. Be the hero in your own spine-tingling epic of action, tension, and terror...and discover the true meaning of F.E.A.R.

F.E.A.R. is more graphically intensive. While being clocked around the same speed as the AMD K8 it still manages to clear out a few FPS ahead and well above the Netburst despite a 1GHz less clock rate.

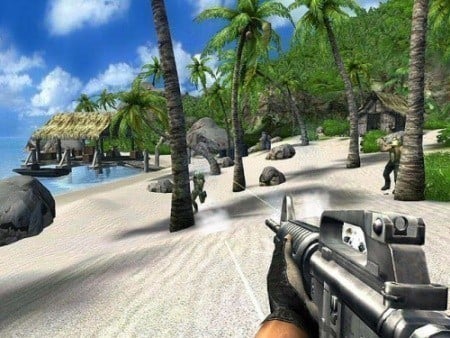

Benchmarks - Far Cry

Far Cry

Version and / or Patch Used: 1.3

Timedemo or Level Used: Benchemall Default

Developer Homepage: http://www.crytek.com

Product Homepage: http://www.farcrygame.com

Buy It Here

While Far Cry is now one of our older benchmarking games, it is still able to put pressure on most computers systems. Utilizing PS2.0 technology with the latest versions supporting Shader Model 3.0 with DX9c and offering an exceptional visual experience, there is no denying that even some of the faster graphics cards get a bit of a workout.

Our last test shows us that Core 2 really has the stuff even in the older games.

Final Thoughts

Intel has finally stepped away from Netburst and its about time too. In the beginning it was clear that Pentium 4's architecture wasn't going to be the ultimate in CPU technology - if a 1.3GHz clocked Pentium 3 could beat it in 90% of benchmarks, AMD's K7 technology was going to be able to kill it, and it did.

Now Intel has finally gotten the idea that just because you have a higher clocked processor doesn't mean you are going to win the benchmarks, especially if the architecture driving this can't keep up with the demands.

Core Architecture is just what the PC doctor ordered, and if this could have been done instead of the Netburst architecture, AMD might not have the market share it does today.

Overall we have seen that Core Duo for mobile has proven to produce the numbers, and Core 2 for the desktop offers great performance in applications and games - it does seem like it is Intel's day to shine. If Intel's trends of adding in further additions down the line still manifests on Core Architecture we are bound to see some interesting times for the future of Core.

United

States: Find other tech and computer products like this

over at

United

States: Find other tech and computer products like this

over at  United

Kingdom: Find other tech and computer products like this

over at

United

Kingdom: Find other tech and computer products like this

over at  Australia:

Find other tech and computer products like this over at

Australia:

Find other tech and computer products like this over at  Canada:

Find other tech and computer products like this over at

Canada:

Find other tech and computer products like this over at  Deutschland:

Finde andere Technik- und Computerprodukte wie dieses auf

Deutschland:

Finde andere Technik- und Computerprodukte wie dieses auf